6.1 مقدمة

أجهزة الكمبيوتر الحديثة للأغراض العامة هي من نوعين: CISC و RISC. يعنيCISC كمبيوتر مجموعة التعليمات المعقدة. يعنيRISK اختصار مجموعة التعليمات للكمبيوتر. تشبه المعالجات الدقيقة 6502 أو 6510، كما تنطبق على كمبيوتر Commodore-64، بنية RISC أكثر من بنية CISC.

تحتوي أجهزة كمبيوتر RISC عمومًا على تعليمات لغة تجميع أقصر (حسب عدد البايتات) مقارنةً بأجهزة كمبيوتر CISC.

ملحوظة : سواء كنت تتعامل مع CISC أو RISC أو الكمبيوتر القديم، يبدأ الجهاز الطرفي من منفذ داخلي ويتجه للخارج عبر منفذ خارجي على السطح الرأسي لوحدة نظام الكمبيوتر (الوحدة الأساسية) وإلى الجهاز الخارجي.

يمكن رؤية التعليمات النموذجية لجهاز كمبيوتر CISC مثل دمج عدة تعليمات قصيرة للغة التجميع في تعليمات لغة تجميع واحدة أطول مما يجعل التعليمات الناتجة معقدة. على وجه الخصوص، يقوم كمبيوتر CISC بتحميل المعاملات من الذاكرة إلى سجلات المعالجات الدقيقة، وينفذ عملية، ثم يخزن النتيجة مرة أخرى في الذاكرة، كل ذلك في تعليمات واحدة. من ناحية أخرى، هذه على الأقل ثلاثة تعليمات (قصيرة) لجهاز الكمبيوتر RISC.

هناك سلسلتان شائعتان من أجهزة كمبيوتر CISC: أجهزة الكمبيوتر ذات المعالجات الدقيقة Intel وأجهزة الكمبيوتر ذات المعالجات الدقيقة AMD. AMD تعني الأجهزة الدقيقة المتقدمة؛ وهي شركة تصنيع أشباه الموصلات. سلسلة معالجات إنتل الدقيقة، حسب ترتيب التطوير، هي 8086، 8088، 80186، 80286، 80386، 80486، بنتيوم، كور، سلسلة آي، سيليرون، وزيون. تعليمات لغة التجميع لمعالجات إنتل الدقيقة المبكرة مثل 8086 و8088 ليست معقدة للغاية. ومع ذلك، فهي معقدة بالنسبة للمعالجات الدقيقة الجديدة. معالجات AMD الحديثة لسلسلة CISC هي Ryzen وOpteron وAthlon وTurion وPhenom وSempron. تُعرف معالجات Intel و AMD الدقيقة بالمعالجات الدقيقة x86.

يعنيARM آلة RISC المتقدمة. تحدد بنيات ARM عائلة من معالجات RISC المناسبة للاستخدام في مجموعة واسعة من التطبيقات. في حين يتم استخدام العديد من معالجات Intel وAMD الدقيقة في أجهزة الكمبيوتر الشخصية المكتبية، فإن العديد من معالجات ARM تعمل كمعالجات مضمنة في أنظمة السلامة الحرجة مثل الفرامل المانعة للانغلاق في السيارات وكمعالجات للأغراض العامة في الساعات الذكية والهواتف المحمولة والأجهزة اللوحية وأجهزة الكمبيوتر المحمولة. . على الرغم من أنه يمكن رؤية كلا النوعين من المعالجات الدقيقة في الأجهزة الصغيرة والكبيرة، إلا أن المعالجات الدقيقة RISC توجد في الأجهزة الصغيرة أكثر من الأجهزة الكبيرة.

كلمة الكمبيوتر

إذا قيل أن جهاز الكمبيوتر عبارة عن جهاز كمبيوتر مكون من 32 بت، فهذا يعني أنه يتم تخزين المعلومات ونقلها ومعالجتها في شكل رموز ثنائية مكونة من 32 بت داخل الجزء الداخلي من اللوحة الأم. ويعني أيضًا أن سجلات الأغراض العامة في المعالج الدقيق للكمبيوتر يبلغ عرضها 32 بت. تعد السجلات A وX وY الخاصة بالمعالج الدقيق 6502 بمثابة سجلات للأغراض العامة. يبلغ عرضها ثمانية بتات، وبالتالي فإن كمبيوتر Commodore-64 هو كمبيوتر مكون من ثمانية بتات.

بعض المفردات

أجهزة الكمبيوتر X86

معاني البايت والكلمة والكلمة المزدوجة والكلمة الرباعية والكلمة الرباعية المزدوجة هي كما يلي بالنسبة لأجهزة الكمبيوتر التي تعمل بنظام التشغيل x86:

- بايت : 8 بت

- كلمة : 16 بت

- كلمة مزدوجة : 32 بت

- رباعية : 64 بت

- رباعية مزدوجة : 128 بت

أجهزة الكمبيوتر ARM

معاني البايت والكلمة النصفية والكلمة والكلمة المزدوجة هي كما يلي لأجهزة كمبيوتر ARM:

- بايت : 8 بت

- تصبح نصف : 16 بت

- كلمة : 32 بت

- كلمة مزدوجة : 64 بت

يجب ملاحظة الاختلافات والتشابهات بين أسماء (وقيم) x86 وARM.

ملحوظة : الأعداد الصحيحة في كلا النوعين من أجهزة الكمبيوتر هي تكملة اثنين.

موقع الذاكرة

في كمبيوتر Commodore-64، يكون موقع الذاكرة عادةً بايت واحد ولكن قد يكون بايتين متتاليين في بعض الأحيان عند النظر في المؤشرات (عنونة غير مباشرة). مع جهاز كمبيوتر حديث x86، يكون موقع الذاكرة 16 بايت متتالية عند التعامل مع كلمة رباعية مزدوجة 16 بايت (128 بت)، و8 بايت متتالية عند التعامل مع كلمة رباعية مكونة من 8 بايت (64 بت)، و4 بايت متتالية عند التعامل مع كلمة رباعية مكونة من 8 بايت (64 بت). 4 بايت (32 بت)، و2 بايت متتاليين عند التعامل مع كلمة مكونة من 2 بايت (16 بت)، و1 بايت عند التعامل مع بايت (8 بت). في حاسوب ARM الحديث، يكون موقع الذاكرة 8 بايت متتالية عند التعامل مع كلمة مزدوجة 8 بايت (64 بت)، و4 بايت متتالية عند التعامل مع كلمة مكونة من 4 بايت (32 بت)، و2 بايت متتاليتين عند التعامل مع كلمة نصف كلمة. 2 بايت (16 بت)، و1 بايت عند التعامل مع بايت (8 بت).

يشرح هذا الفصل ما هو شائع في بنيات CISC وRISC وما هي الاختلافات بينهما. ويتم ذلك بالمقارنة مع الكمبيوتر 6502 μP والكمبيوتر commodore-64 حيثما يكون ذلك قابلاً للتطبيق.

6.2 مخطط كتلة اللوحة الأم للكمبيوتر الحديث

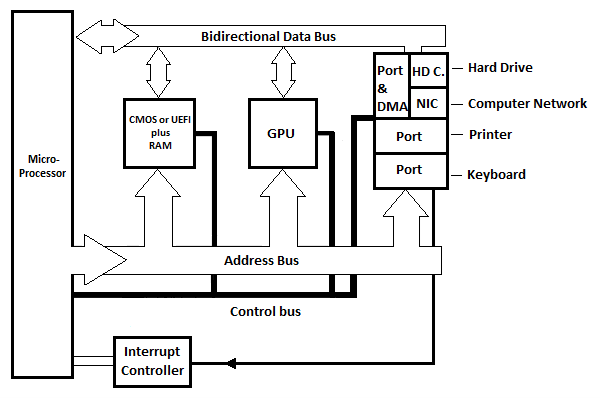

PC لتقف على الكمبيوتر الشخصي. فيما يلي رسم تخطيطي أساسي عام للوحة الأم الحديثة المزودة بمعالج دقيق واحد للكمبيوتر الشخصي. وهو يمثل اللوحة الأم CISC أو RISC.

الشكل 6.21 الرسم التخطيطي الأساسي للوحة الأم للكمبيوتر الحديث

يظهر في الرسم البياني ثلاثة منافذ داخلية، ولكن هناك المزيد في الواقع العملي. يحتوي كل منفذ على سجل يمكن اعتباره المنفذ نفسه. تحتوي كل دائرة منفذ على سجل آخر على الأقل يمكن أن يسمى 'سجل الحالة'. يشير سجل الحالة إلى منفذ البرنامج الذي يرسل إشارة المقاطعة إلى المعالج الدقيق. توجد دائرة تحكم في المقاطعة (غير موضحة) تفرق بين خطوط المقاطعة المختلفة من المنافذ المختلفة وتحتوي على بضعة أسطر فقط إلى μP.

HD.C في الرسم البياني يرمز إلى بطاقة القرص الصلب. NIC يعني بطاقة واجهة الشبكة. يتم توصيل بطاقة (دائرة) القرص الصلب بالقرص الصلب الموجود داخل الوحدة الأساسية (وحدة النظام) للكمبيوتر الحديث. يتم توصيل بطاقة واجهة الشبكة (الدائرة) عبر كابل خارجي بجهاز كمبيوتر آخر. يوجد في الرسم التخطيطي منفذ واحد وDMA (راجع الرسم التوضيحي التالي) متصلين ببطاقة القرص الصلب و/أو ببطاقة واجهة الشبكة. يرمز DMA إلى الوصول المباشر إلى الذاكرة.

تذكر من فصل الكمبيوتر Commodore-64 أنه من أجل إرسال البايتات من الذاكرة إلى محرك الأقراص أو كمبيوتر آخر، يجب نسخ كل بايت إلى سجل في المعالج الدقيق قبل نسخها إلى المنفذ الداخلي المقابل، ثم يتم نسخها تلقائيًا بعد ذلك. إلى الجهاز. من أجل استقبال البايتات من محرك الأقراص أو كمبيوتر آخر إلى الذاكرة، يجب نسخ كل بايت من سجل المنفذ الداخلي المقابل إلى سجل المعالجات الدقيقة قبل نسخها إلى الذاكرة. يستغرق هذا عادةً وقتًا طويلاً إذا كان عدد البايتات في الدفق كبيرًا. الحل للنقل السريع هو استخدام الوصول المباشر للذاكرة (الدائرة) دون المرور عبر المعالج الدقيق.

تقع دائرة DMA بين المنفذ وHD. ج أو نيك. مع الوصول المباشر إلى الذاكرة لدائرة DMA، يتم نقل تدفقات كبيرة من البايتات مباشرة بين دائرة DMA والذاكرة (RAM) دون استمرار مشاركة المعالج الدقيق. يستخدم DMA ناقل العناوين وناقل البيانات بدلاً من μP. تكون المدة الإجمالية للنقل أقصر مما إذا كان سيتم استخدام μP الثابت. يستخدم كل من HD C. أو NIC DMA عندما يكون لديهم دفق كبير من البيانات (البايت) للنقل باستخدام ذاكرة الوصول العشوائي (الذاكرة).

يشير GPU إلى وحدة معالجة الرسومات. هذه الكتلة الموجودة على اللوحة الأم مسؤولة عن إرسال النص والصور المتحركة أو الثابتة إلى الشاشة.

مع أجهزة الكمبيوتر الحديثة (PCs)، لا توجد ذاكرة للقراءة فقط (ROM). ومع ذلك، هناك BIOS أو UEFI وهو نوع من ذاكرة الوصول العشوائي غير المتطايرة. يتم بالفعل الاحتفاظ بالمعلومات الموجودة في BIOS بواسطة بطارية. البطارية هي في الواقع ما يحافظ على مؤقت الساعة أيضًا، في الوقت والتاريخ المناسبين للكمبيوتر. تم اختراع UEFI بعد BIOS، وقد حل محل BIOS على الرغم من أن BIOS لا يزال مناسبًا تمامًا في أجهزة الكمبيوتر الحديثة. سنناقش المزيد حول هذه الأمور لاحقًا!

في أجهزة الكمبيوتر الحديثة، لا تعد نواقل العناوين والبيانات بين μP ودوائر المنافذ الداخلية (والذاكرة) نواقل متوازية. وهي عبارة عن حافلات تسلسلية تحتاج إلى موصلين للنقل في اتجاه واحد وموصلين آخرين للنقل في الاتجاه المعاكس. وهذا يعني، على سبيل المثال، أنه يمكن إرسال 32 بت في سلسلة (بت تلو الآخر) في أي من الاتجاهين.

إذا كان الإرسال التسلسلي في اتجاه واحد فقط مع موصلين (خطين)، فيُقال أنه أحادي الاتجاه. إذا كان الإرسال التسلسلي في كلا الاتجاهين بأربعة موصلات، وزوج واحد في أي اتجاه، يُقال أن هذا الإرسال مزدوج الاتجاه.

لا تزال الذاكرة الكاملة للكمبيوتر الحديث تتكون من سلسلة من مواقع البايت: ثمانية بتات لكل بايت. يحتوي الكمبيوتر الحديث على مساحة ذاكرة لا تقل عن 4 جيجا بايت = 4 × 210 × 2 10 × 2 10 = 4 × 1,073,741,824 10 بايت = 4 × 1024 10/فرعي> × 1024 10 × 1024 10 = 4 × 1,073,741,824 10 .

ملحوظة : على الرغم من عدم ظهور أي دائرة مؤقت على اللوحة الأم السابقة، إلا أن جميع اللوحات الأم الحديثة تحتوي على دوائر مؤقت.

6.3 أساسيات هندسة الكمبيوتر x64

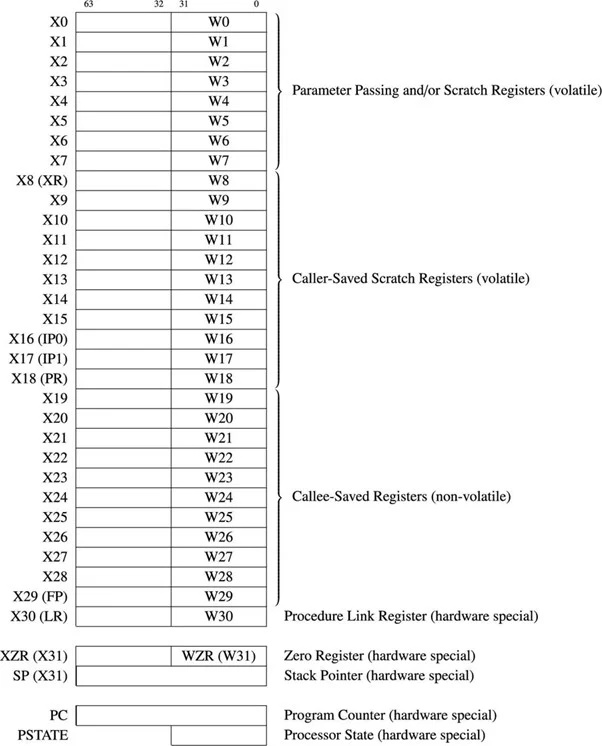

6.31 مجموعة التسجيل x64

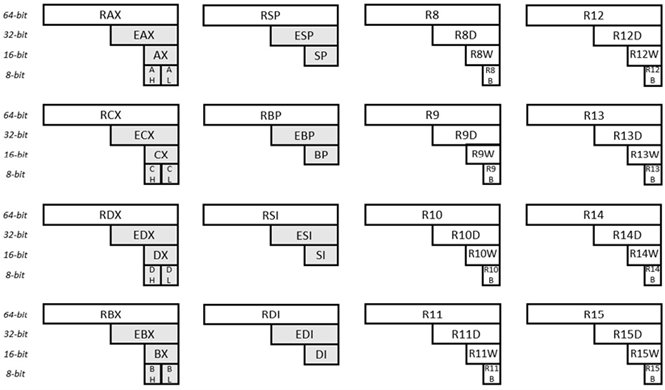

المعالج الدقيق 64 بت من سلسلة المعالجات الدقيقة x86 هو معالج دقيق 64 بت. من الحديث تمامًا استبدال معالج 32 بت من نفس السلسلة. سجلات الأغراض العامة للمعالج الدقيق 64 بت وأسمائها هي كما يلي:

الشكل 6.31 سجلات الأغراض العامة لـ x64

يظهر في الرسم التوضيحي ستة عشر (16) سجلاً للأغراض العامة. يبلغ عرض كل من هذه السجلات 64 بت. بالنظر إلى السجل الموجود في الزاوية العلوية اليسرى، يتم تحديد الـ 64 بت على أنها RAX. يتم تعريف أول 32 بت من هذا السجل نفسه (من اليمين) على أنها EAX. يتم تعريف أول 16 بت من هذا السجل نفسه (من اليمين) على أنها AX. يتم تعريف البايت الثاني (من اليمين) من نفس السجل بـ AH (H هنا يعني عالي). ويتم تعريف البايت الأول (من نفس السجل) على أنه AL (يعني L هنا منخفض). بالنظر إلى السجل الموجود في الزاوية اليمنى السفلية، يتم تحديد الـ 64 بت على أنها R15. يتم تعريف أول 32 بت من هذا السجل نفسه باسم R15D. يتم تعريف أول 16 بت من هذا السجل نفسه باسم R15W. ويتم تعريف البايت الأول على أنه R15B. يتم شرح أسماء السجلات الأخرى (والسجلات الفرعية) بالمثل.

هناك بعض الاختلافات بين Intel وAMD μPs. المعلومات الواردة في هذا القسم مخصصة لشركة Intel.

مع 6502 μP، يبلغ عرض سجل عداد البرامج (الذي لا يمكن الوصول إليه مباشرة) والذي يحمل التعليمات التالية المراد تنفيذها 16 بت. هنا (x64)، يسمى عداد البرنامج مؤشر التعليمات، ويبلغ عرضه 64 بت. تم تصنيفه على أنه RIP. هذا يعني أن x64 μP يمكنه معالجة ما يصل إلى 264 = 1.844674407 × 1019 (في الواقع 18,446,744,073,709,551,616) من مواقع بايت الذاكرة. RIP ليس سجلاً للأغراض العامة.

يعد Stack Pointer Register أو RSP من بين 16 سجلًا للأغراض العامة. يشير إلى آخر إدخال في المكدس في الذاكرة. كما هو الحال مع 6502 μP، فإن حزمة x64 تنمو للأسفل. مع x64، يتم استخدام المكدس الموجود في ذاكرة الوصول العشوائي (RAM) لتخزين عناوين الإرجاع للإجراءات الفرعية. كما أنها تستخدم لتخزين 'مساحة الظل' (راجع المناقشة التالية).

يحتوي 6502 μP على سجل حالة معالج 8 بت. ما يعادله في x64 يسمى سجل RFLAGS. يقوم هذا السجل بتخزين العلامات المستخدمة لنتائج العمليات وللتحكم في المعالج (μP). يبلغ عرضه 64 بت. يتم حجز الـ 32 بت الأعلى ولا يتم استخدامها حاليًا. يعطي الجدول التالي الأسماء والفهرس والمعاني للبتات شائعة الاستخدام في سجل RFLAGS:

| الجدول 6.31.1 أعلام RFLAGS الأكثر استخدامًا (البتات) |

|||

|---|---|---|---|

| رمز | قليل | اسم | غاية |

| قوات التحالف | 0 | يحمل | يتم تعيينه إذا كانت العملية الحسابية تولد ترحيلاً أو اقتراضًا من الجزء الأكثر أهمية من النتيجة؛ مسح خلاف ذلك. تشير هذه العلامة إلى حالة تجاوز السعة للحسابات ذات الأعداد الصحيحة غير الموقعة. كما أنها تستخدم في العمليات الحسابية متعددة الدقة. |

| الجبهة الوطنية | 2 | التكافؤ | يتم تعيينه إذا كان البايت الأقل أهمية من النتيجة يحتوي على عدد زوجي من 1 بت؛ مسح خلاف ذلك. |

| ل | 4 | يُعدِّل | يتم تعيينه إذا كانت العملية الحسابية تولد ترحيلًا أو استعارة من البتة 3 من النتيجة؛ مسح خلاف ذلك. تُستخدم هذه العلامة في العمليات الحسابية العشرية ذات الترميز الثنائي (BCD). |

| ZF | 6 | صفر | يتم تعيينه إذا كانت النتيجة صفر؛ مسح خلاف ذلك. |

| سادس | 7 | لافتة | يتم تعيينه إذا كان يساوي البت الأكثر أهمية في النتيجة وهو بت الإشارة لعدد صحيح موقّع (يشير 0 إلى قيمة موجبة ويشير 1 إلى قيمة سالبة). |

| ل | أحد عشر | تجاوز | يتم تعيينه إذا كانت نتيجة العدد الصحيح كبيرة جدًا رقمًا موجبًا أو صغيرة جدًا رقمًا سالبًا (باستثناء بت الإشارة) بحيث لا تتناسب مع المعامل الوجهة؛ مسح خلاف ذلك. تشير هذه العلامة إلى حالة تجاوز السعة لحساب العدد الصحيح الموقع (مكمل اثنين). |

| مدافع | 10 | اتجاه | يتم ضبطه إذا كانت تعليمات سلسلة الاتجاه تعمل (زيادة أو نقصان). |

| بطاقة تعريف | واحد وعشرين | تعريف | يتم تعيينه إذا كانت قابلية التغيير تشير إلى وجود تعليمات CPUID. |

بالإضافة إلى السجلات الثمانية عشر ذات 64 بت التي تمت الإشارة إليها مسبقًا، تحتوي بنية x64 μP على ثمانية سجلات بعرض 80 بت لحساب النقطة العائمة. يمكن أيضًا استخدام هذه السجلات الثمانية كسجلات MMX (راجع المناقشة التالية). يوجد أيضًا ستة عشر سجلاً بحجم 128 بت لـ XMM (راجع المناقشة التالية).

هذا ليس كل شيء عن السجلات. هناك المزيد من سجلات x64 وهي سجلات المقاطع (غير مستخدمة في الغالب في x64)، وسجلات التحكم، وسجلات إدارة الذاكرة، وسجلات تصحيح الأخطاء، وسجلات المحاكاة الافتراضية، وسجلات الأداء التي تتبع جميع أنواع المعلمات الداخلية (ضربات/أخطاء ذاكرة التخزين المؤقت، والعمليات الصغيرة المنفذة، والتوقيت ، وأكثر بكثير).

SIMD

يعنيSIMD بيانات متعددة للتعليمات الفردية. وهذا يعني أن تعليمات لغة التجميع الواحدة يمكن أن تعمل على بيانات متعددة في نفس الوقت في معالج دقيق واحد. خذ بعين الاعتبار الجدول التالي:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| + | 9 | 10 | أحد عشر | 12 | 13 | 14 | خمسة عشر | 16 |

| = | 10 | 12 | 14 | 16 | 18 | عشرين | 22 | 24 |

في هذا الجدول، تتم إضافة ثمانية أزواج من الأرقام بالتوازي (في نفس المدة) لإعطاء ثمانية إجابات. يمكن لتعليمة لغة تجميع واحدة إجراء إضافات الأعداد الصحيحة الثمانية المتوازية في سجلات MMX. يمكن فعل شيء مماثل مع سجلات XMM. لذلك، هناك تعليمات MMX للأعداد الصحيحة وتعليمات XMM للعوامات.

6.32 خريطة الذاكرة وx64

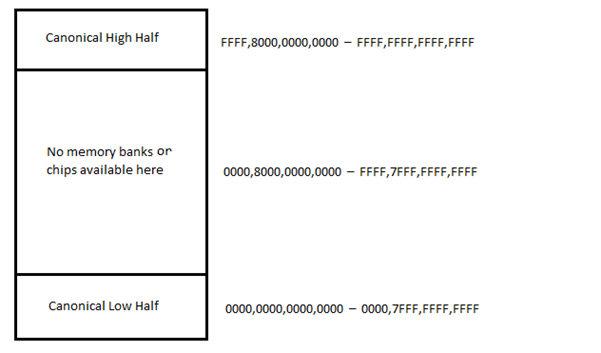

مع وجود مؤشر التعليمات (عداد البرامج) الذي يحتوي على 64 بت، فهذا يعني أنه يمكن معالجة مواقع بايت الذاكرة 264 = 1.844674407 × 1019. في النظام الست عشري، أعلى موقع بايت هو FFFF، FFFF، FFFF، FFFF16. لا يوجد كمبيوتر عادي اليوم يمكنه توفير مثل هذه المساحة الكبيرة من الذاكرة (الكاملة). لذا فإن خريطة الذاكرة المناسبة لجهاز الكمبيوتر x64 هي كما يلي:

لاحظ أن الفجوة من 0000,8000,0000,000016 إلى FFFF,7FFF,FFFF,FFFF16 لا تحتوي على مواقع ذاكرة (لا توجد بنوك ذاكرة الوصول العشوائي). هذا فرق قدره FFFF,0000,0000,000116 وهو كبير جدًا. النصف الأعلى الكنسي يحتوي على نظام التشغيل، في حين أن النصف الأدنى الكنسي يحتوي على برامج المستخدم (التطبيقات) والبيانات. يتكون نظام التشغيل من جزأين: UEFI (BIOS) صغير وجزء كبير يتم تحميله من القرص الصلب. يتحدث الفصل التالي أكثر عن أنظمة التشغيل الحديثة. لاحظ التشابه مع خريطة الذاكرة هذه وتلك الخاصة بـ Commodore-64 عندما قد يبدو أن 64 كيلو بايت عبارة عن ذاكرة كبيرة.

في هذا السياق، يُطلق على نظام التشغيل تقريبًا اسم 'النواة'. النواة مشابهة للنواة الخاصة بجهاز الكمبيوتر Commodore-64، ولكنها تحتوي على إجراءات فرعية أكثر بكثير.

إن endianness لـ x64 هو endian صغير، مما يعني أنه بالنسبة للموقع، يشير العنوان السفلي إلى بايت محتوى أقل في الذاكرة.

6.33 أوضاع معالجة لغة التجميع لـ x64

أوضاع العنونة هي الطرق التي يمكن للتعليمات من خلالها الوصول إلى سجلات μP والذاكرة (بما في ذلك سجلات المنفذ الداخلي). يحتوي x64 على العديد من أوضاع العنونة، ولكن يتم هنا تناول أوضاع العنونة شائعة الاستخدام فقط. بناء الجملة العام للتعليمة هنا هو:

وجهة كود التشغيل، المصدر

تتم كتابة الأرقام العشرية دون أي بادئة أو لاحقة. مع 6502، المصدر ضمني. يحتوي x64 على رموز تشغيلية أكثر من 6502، لكن بعض رموز التشغيل لها نفس أساليب الإستذكار. تعليمات x64 الفردية ذات طول متغير ويمكن أن يتراوح حجمها من 1 إلى 15 بايت. أوضاع العنونة شائعة الاستخدام هي كما يلي:

وضع المعالجة الفورية

هنا، المعامل المصدر هو قيمة فعلية وليس عنوانًا أو تسمية. مثال (اقرأ التعليق):

أضف إياكس، 14؛ أضف العلامة العشرية 14 إلى EAX 32 بت من RAX 64 بت، وتبقى الإجابة في EAX (الوجهة)

قم بالتسجيل لتسجيل وضع العنونة

مثال:

إضافة R8B، AL ; إضافة 8 بت AL من RAX إلى R8B من 64 بت R8 - تبقى الإجابات في R8B (الوجهة)

وضع العنونة غير المباشرة والمفهرسة

تعني المعالجة غير المباشرة باستخدام 6502 μP أن موقع العنوان المحدد في التعليمات له العنوان الفعال (المؤشر) للموقع النهائي. يحدث شيء مماثل مع x64. تعني معالجة الفهرس باستخدام 6502 μP أنه تتم إضافة محتوى سجل μP إلى العنوان المحدد في التعليمات للحصول على العنوان الفعال. يحدث شيء مماثل مع x64. أيضًا، مع x64، يمكن أيضًا ضرب محتوى السجل بـ 1 أو 2 أو 4 أو 8 قبل إضافته إلى العنوان المحدد. يمكن أن تجمع تعليمات mov (النسخة) الخاصة بـ x64 بين العنونة غير المباشرة والمفهرسة. مثال:

موف R8W، 1234[8*RAX+RCX]؛ انقل الكلمة إلى العنوان (8 x RAX + RCX) + 1234

هنا، يحتوي R8W على أول 16 بت من R8. العنوان المحدد هو 1234. يحتوي سجل RAX على رقم 64 بت مضروبًا في 8. وتتم إضافة النتيجة إلى محتوى سجل RCX 64 بت. تتم إضافة هذه النتيجة الثانية إلى العنوان المحدد وهو 1234 للحصول على العنوان الفعال. يتم نقل (نسخ) الرقم الموجود في موقع العنوان الفعال إلى أول مكان مكون من 16 بت (R8W) من سجل R8، ليحل محل كل ما كان موجودًا. لاحظ استخدام الأقواس المربعة. تذكر أن الكلمة في x64 يبلغ عرضها 16 بت.

RIP عنونة نسبية

بالنسبة إلى 6502 μP، يتم استخدام العنونة النسبية فقط مع تعليمات الفرع. هناك، المعامل الوحيد لكود التشغيل هو الإزاحة التي تتم إضافتها أو طرحها لمحتوى عداد البرنامج لعنوان التعليمات الفعال (وليس عنوان البيانات). يحدث شيء مشابه مع الإصدار x64 حيث يُطلق على عداد البرامج اسم 'مؤشر التعليمات'. لا يجب أن تكون التعليمات باستخدام x64 مجرد تعليمات فرعية. مثال على العنونة النسبية لـ RIP هو:

موف آل، [ريب]

يحتوي AL of RAX على رقم موقع 8 بت يتم إضافته أو طرحه من المحتوى الموجود في RIP (مؤشر تعليمات 64 بت) للإشارة إلى التعليمات التالية. لاحظ أنه يتم تبديل المصدر والوجهة بشكل استثنائي في هذه التعليمات. لاحظ أيضًا استخدام الأقواس المربعة التي تشير إلى محتوى RIP.

6.34 التعليمات الشائعة الاستخدام لـ x64

في الجدول التالي * تعني اللواحق المحتملة المختلفة لمجموعة فرعية من أكواد التشغيل:

| الجدول 6.34.1 التعليمات الشائعة الاستخدام في x64 |

|

|---|---|

| رمز التشغيل | معنى |

| وسائل التحقق | نقل (نسخ) من/إلى/بين الذاكرة والسجلات |

| كموف* | التحركات الشرطية المختلفة |

| XCHG | تبادل |

| BSWAP | مبادلة البايت |

| دفع البوب | استخدام المكدس |

| إضافة/ADC | إضافة/مع حمل |

| فرعي/SBC | طرح / مع حمل |

| مول/إيمول | ضرب / غير موقعة |

| DIV/IDIV | تقسيم / غير موقعة |

| المؤتمر الوطني العراقي/ديسمبر | زيادة / إنقاص |

| نيج | نفي |

| CMP | يقارن |

| و/أو/XOR/NOT | عمليات البت |

| شار/ريال سعودي | التحول الصحيح المنطقي/الحسابي |

| ش.ل/ش.م.ل | التحول إلى اليسار المنطقي/الحسابي |

| معدل العائد/الدور | تدوير اليمين / اليسار |

| آر سي آر / آر سي إل | قم بتدوير اليمين/اليسار من خلال لقمة الحمل |

| بي تي/بي تي إس/بي تي آر | اختبار البت/وضبط/وإعادة التعيين |

| أحزاب اللقاء المشترك | القفز غير المشروط |

| جي/JNE/JC/JNC/J* | القفز إذا كان متساويا / غير متساو / يحمل / لا يحمل / العديد من الآخرين |

| المشي / المشي / المشي | حلقة مع ECX |

| الاتصال/إعادة الاتصال | استدعاء روتين فرعي/العودة |

| لا | لايوجد عملية |

| CPUID | معلومات وحدة المعالجة المركزية |

يحتوي x64 على تعليمات الضرب والقسمة. يحتوي على دوائر أجهزة الضرب والقسمة في μP. لا يحتوي الطراز 6502 μP على دوائر أجهزة الضرب والقسمة. يعد إجراء الضرب والقسمة بواسطة الأجهزة أسرع من إجراء عملية الضرب والقسمة بواسطة البرامج (بما في ذلك نقل البتات).

تعليمات السلسلة

هناك عدد من تعليمات السلسلة، ولكن التعليمات الوحيدة التي سيتم مناقشتها هنا هي تعليمات MOVS (لنقل السلسلة) لنسخ سلسلة تبدأ من العنوان C000 ح . للبدء في العنوان C100 ح ، استخدم التعليمات التالية:

تحركات [C100H]، [C000H]

لاحظ اللاحقة H للرقم الست عشري.

6.35 حلقات في x64

يحتوي 6502 μP على تعليمات فرعية للتكرار. تنتقل تعليمات الفرع إلى موقع العنوان الذي يحتوي على التعليمات الجديدة. يمكن أن يسمى موقع العنوان 'حلقة'. يحتوي x64 على تعليمات LOOP/LOOPE/LOOPNE للتكرار. لا ينبغي الخلط بين كلمات لغة التجميع المحجوزة هذه وبين تسمية 'الحلقة' (بدون علامتي الاقتباس). السلوك هو كما يلي:

تعمل LOOP على تقليل ECX والتحقق مما إذا كانت ECX ليست صفرًا. إذا تم استيفاء هذا الشرط (صفر)، فإنه ينتقل إلى تسمية محددة. وإلا فإنه سيفشل (تابع بقية التعليمات في المناقشة التالية).

يقوم LOOPE بتخفيض ECX والتحقق من أن ECX ليس صفرًا (قد يكون 1 على سبيل المثال) ويتم ضبط ZF (على 1). إذا تم استيفاء هذه الشروط، فإنه يقفز على التسمية. وإلا فإنه يسقط.

يقوم LOOPNE بتخفيض ECX والتحقق من أن ECX ليس صفرًا وأن ZF غير مضبوط (أي يكون صفرًا). إذا تم استيفاء هذه الشروط، فإنه ينتقل إلى التسمية. وإلا فإنه يسقط.

مع x64، فإن سجل RCX أو أجزائه الفرعية مثل ECX أو CX، يحمل عددًا صحيحًا للعداد. باستخدام تعليمات LOOP، يقوم العداد عادةً بالعد التنازلي، ويتناقص بمقدار 1 لكل قفزة (حلقة). في مقطع التعليمات البرمجية التكراري التالي، يزداد الرقم الموجود في سجل EAX من 0 إلى 10 في عشر تكرارات بينما يتناقص الرقم في ECX (يتناقص) 10 مرات (اقرأ التعليقات):

موف إياكس، 0؛

موف إي سي إكس، 10؛ قم بالعد التنازلي 10 مرات بشكل افتراضي، مرة واحدة لكل تكرار

ملصق:

إنك إياكس ; زيادة EAX كجسم الحلقة

تسمية الحلقة؛ إنقاص EAX، وإذا لم تكن EAX صفرًا، فأعد تنفيذ نص الحلقة من 'label:'

يبدأ ترميز الحلقة من 'التسمية:'. لاحظ استخدام القولون. ينتهي ترميز الحلقة بـ 'LOOP label' الذي يشير إلى إنقاص EAX. إذا لم يكن محتواه صفرًا، فارجع إلى التعليمات بعد 'label:' وأعد تنفيذ أي تعليمات (جميع تعليمات الجسم) التي تأتي للأسفل حتى 'LOOP label'. لاحظ أن 'التسمية' لا يزال من الممكن أن يكون لها اسم آخر.

6.36 الإدخال/الإخراج لـ x64

يتناول هذا القسم من الفصل إرسال البيانات إلى منفذ الإخراج (الداخلي) أو استقبال البيانات من منفذ الإدخال (الداخلي). تحتوي مجموعة الشرائح على منافذ ذات ثمانية بتات. يمكن التعامل مع أي منفذين متتاليين 8 بت كمنفذ 16 بت، وأي أربعة منافذ متتالية يمكن أن تكون منفذ 32 بت. وبهذه الطريقة، يمكن للمعالج نقل 8 أو 16 أو 32 بت من وإلى جهاز خارجي.

يمكن نقل المعلومات بين المعالج ومنفذ داخلي بطريقتين: استخدام ما يعرف بالإدخال/الإخراج المعين للذاكرة أو باستخدام مساحة عنوان إدخال/إخراج منفصلة. يشبه الإدخال / الإخراج المعين للذاكرة ما يحدث مع المعالج 6502 حيث تكون عناوين المنافذ في الواقع جزءًا من مساحة الذاكرة بأكملها. في هذه الحالة، عند إرسال البيانات إلى موقع عنوان معين، فإنها تنتقل إلى منفذ وليس إلى بنك الذاكرة. قد تحتوي المنافذ على مساحة عنوان إدخال/إخراج منفصلة. في هذه الحالة الأخيرة، جميع بنوك الذاكرة لها عناوينها من الصفر. يوجد نطاق عنوان منفصل من 0000H إلى FFFF16. يتم استخدامها بواسطة المنافذ الموجودة في مجموعة الشرائح. تمت برمجة اللوحة الأم بحيث لا يتم الخلط بين الإدخال/الإخراج المعين للذاكرة ومساحة عنوان الإدخال/الإخراج المنفصلة.

الإدخال/الإخراج المعين للذاكرة

وبهذا، تعتبر المنافذ بمثابة مواقع للذاكرة، ويتم استخدام رموز التشغيل العادية المستخدمة بين الذاكرة وμP لنقل البيانات بين μP والمنافذ. لذلك، لنقل بايت من منفذ على العنوان F000H إلى سجل μP RAX:EAX:AX:AL، قم بما يلي:

موف آل، [F000H]

يمكن نقل السلسلة من الذاكرة إلى المنفذ والعكس. مثال:

موفز [F000H]، [C000H]؛ المصدر هو C000H، والوجهة هي المنفذ في F000H.

مساحة عنوان الإدخال/الإخراج منفصلة

مع هذا، يجب استخدام التعليمات الخاصة للإدخال والإخراج.

نقل العناصر الفردية

سجل المعالج للنقل هو RAX. في الواقع، إنه RAX:EAX للكلمة المزدوجة، وRAX:EAX:AX للكلمة، وRAX:EAX:AX:AL للبايت. لذلك، لنقل بايت من منفذ في FFF0h، إلى RAX:EAX:AX:AL، اكتب ما يلي:

في آل، [FFF0H]

للتحويل العكسي، اكتب ما يلي:

خارج [FFF0H]، آل

لذلك، بالنسبة للعناصر الفردية، تكون التعليمات موجودة وخارجًا. يمكن أيضًا توفير عنوان المنفذ في سجل RDX:EDX:DX.

نقل السلاسل

يمكن نقل السلسلة من الذاكرة إلى منفذ مجموعة الشرائح والعكس. لنقل سلسلة من منفذ على العنوان FFF0H إلى الذاكرة، ابدأ من C100H، اكتب:

إنس [ESI]، [DX]

والذي له نفس التأثير مثل:

INS [EDI]، [DX]

يجب على المبرمج وضع عنوان المنفذ ثنائي البايت لـ FFF0H في سجل RDX:EDX:Dx، ويجب أن يضع عنوان المنفذ ثنائي البايت لـ C100H في سجل RSI:ESI أو RDI:EDI. بالنسبة للتحويل العكسي، قم بما يلي:

INS [DX]، [ESI]

والذي له نفس التأثير مثل:

INS [DX]، [EDI]

6.37 المكدس في x64

مثل المعالج 6502، يحتوي المعالج x64 أيضًا على كومة من ذاكرة الوصول العشوائي. يمكن أن يكون المكدس لـ x64 2 16 = 65,536 بايت أو يمكن أن يكون 2 32 = 4,294,967,296 بايت. كما أنها تنمو نحو الأسفل. عندما يتم دفع محتوى السجل إلى المكدس، ينخفض الرقم الموجود في مؤشر مكدس RSP بمقدار 8. تذكر أن عنوان الذاكرة لـ x64 يبلغ عرضه 64 بت. تشير القيمة الموجودة في مؤشر المكدس في μP إلى الموقع التالي في المكدس في ذاكرة الوصول العشوائي (RAM). عندما يتم نقل محتوى السجل (أو قيمة في أحد المعاملات) من المكدس إلى السجل، فإن الرقم الموجود في مؤشر مكدس RSP يزداد بمقدار 8. ويقرر نظام التشغيل حجم المكدس وأين يبدأ في ذاكرة الوصول العشوائي (RAM) وينمو إلى الأسفل. تذكر أن المكدس عبارة عن بنية Last-In-First-Out (LIFO) التي تنمو للأسفل وتتقلص للأعلى في هذه الحالة.

لدفع محتوى سجل μP RBX إلى المكدس، قم بما يلي:

ادفع RBX

لإعادة الإدخال الأخير في المكدس مرة أخرى إلى RBX، قم بما يلي:

بوب ار بي اكس

6.38 الإجراء في x64

يسمى الروتين الفرعي في x64 'الإجراء'. يتم استخدام المكدس هنا أكثر من استخدامه لـ 6502 μP. بناء الجملة لإجراء x64 هو:

اسم المنتج:

هيئة الإجراء

…

يمين

قبل المتابعة، لاحظ أن أكواد التشغيل والتسميات الخاصة بالروتين الفرعي x64 (تعليمات لغة التجميع بشكل عام) غير حساسة لحالة الأحرف. وهذا يعني أن proc_name هو نفس PROC_NAME. مثل 6502، يبدأ اسم الإجراء (التسمية) في بداية سطر جديد في محرر النصوص للغة التجميع. يتبع ذلك نقطتان وليس مسافة ورمز التشغيل كما هو الحال مع 6502. ويتبع الجسم الروتيني الفرعي، وينتهي بـ RET وليس RTS كما هو الحال مع 6502 μP. كما هو الحال مع 6502، كل تعليمات في الجسم، بما في ذلك RET، لا تبدأ في بداية السطر الخاص بها. لاحظ أن التصنيف هنا يمكن أن يزيد طوله عن 8 أحرف. لاستدعاء هذا الإجراء، من أعلى أو أسفل الإجراء المكتوب، قم بما يلي:

اتصل بـ proc_name

مع 6502، يكون اسم الملصق مجرد كتابة للاتصال. ومع ذلك، يتم هنا كتابة الكلمة المحجوزة 'CALL' أو 'call' متبوعة باسم الإجراء (الروتين الفرعي) بعد مسافة.

عند التعامل مع الإجراءات، عادة ما يكون هناك إجراءان. إجراء واحد يستدعي الآخر. الإجراء الذي يتم الاتصال به (الذي يحتوي على تعليمات الاتصال) يسمى 'المتصل'، والإجراء الذي يتم الاتصال به يسمى 'المستدعي'. هناك اتفاقية (قواعد) يجب اتباعها.

قواعد المتصل

يجب على المتصل الالتزام بالقواعد التالية عند استدعاء روتين فرعي:

1. قبل استدعاء روتين فرعي، يجب على المتصل حفظ محتويات بعض السجلات التي تم تعيينها على أنها محفوظة للمتصل في المكدس. السجلات المحفوظة بواسطة المتصل هي R10 وR11 وأي سجلات يتم وضع المعلمات فيها (RDI وRSI وRDX وRCX وR8 وR9). إذا كان سيتم الاحتفاظ بمحتويات هذه السجلات عبر استدعاء الروتين الفرعي، فادفعها إلى المكدس بدلاً من حفظها في ذاكرة الوصول العشوائي (RAM). يجب القيام بذلك لأنه يجب على المستدعي استخدام السجلات لمسح المحتويات السابقة.

2. إذا كان الإجراء هو إضافة رقمين على سبيل المثال، فإن الرقمين هما المعلمات التي سيتم تمريرها إلى المكدس. لتمرير المعلمات إلى الروتين الفرعي، ضع ستة منها في السجلات التالية بالترتيب: RDI، RSI، RDX، RCX، R8، R9. إذا كان هناك أكثر من ستة معلمات في الروتين الفرعي، فادفع الباقي إلى المكدس بترتيب عكسي (أي المعلمة الأخيرة أولاً). نظرًا لنمو المكدس، يتم تخزين أول المعلمات الإضافية (المعلمة السابعة حقًا) في أدنى عنوان (تم استخدام هذا الانعكاس للمعلمات تاريخيًا للسماح بتمرير الوظائف (الروتينات الفرعية) بعدد متغير من المعلمات).

3. للاتصال بالروتين الفرعي (الإجراء)، استخدم تعليمات الاتصال. تضع هذه التعليمات عنوان المرسل أعلى المعلمات الموجودة على المكدس (أدنى موضع) والفروع في رمز الروتين الفرعي.

4. بعد عودة الروتين الفرعي (أي بعد تعليمات الاتصال مباشرة)، يجب على المتصل إزالة أي معلمات إضافية (تتجاوز المعلمات الستة المخزنة في السجلات) من المكدس. يؤدي هذا إلى استعادة المكدس إلى حالته قبل إجراء الاستدعاء.

5. يمكن للمتصل أن يتوقع العثور على القيمة المرجعة (العنوان) للروتين الفرعي في سجل RAX.

6. يستعيد المتصل محتويات السجلات المحفوظة بواسطة المتصل (R10 وR11 وأي سجلات تمرير في المعلمات) عن طريق إخراجها من المكدس. يمكن للمتصل أن يفترض أنه لم يتم تعديل أي سجلات أخرى بواسطة الروتين الفرعي.

نظرًا للطريقة التي تم بها بناء اصطلاح الاستدعاء، عادةً ما لن تؤدي بعض (أو معظم) هذه الخطوات إلى إجراء أي تغييرات على المكدس. على سبيل المثال، إذا كان هناك ستة معلمات أو أقل، فلن يتم دفع أي شيء إلى المكدس في تلك الخطوة. وبالمثل، عادةً ما يحتفظ المبرمجون (والمترجمون) بالنتائج التي يهتمون بها خارج السجلات المحفوظة لدى المتصل في الخطوتين 1 و6 لمنع عمليات الدفع والفرقع الزائدة.

هناك طريقتان أخريان لتمرير المعلمات إلى روتين فرعي، ولكن لن يتم تناولهما في هذه الدورة المهنية عبر الإنترنت. يستخدم أحدهم المكدس نفسه بدلاً من سجلات الأغراض العامة.

قواعد كالي

يجب أن يلتزم تعريف الروتين الفرعي المسمى بالقواعد التالية:

1. قم بتخصيص المتغيرات المحلية (المتغيرات التي تم تطويرها ضمن الإجراء) باستخدام السجلات أو توفير مساحة على المكدس. أذكر المكدس ينمو للأسفل. لذلك، لتوفير مساحة في الجزء العلوي من المكدس، يجب تقليل مؤشر المكدس. يعتمد مقدار تقليل مؤشر المكدس على العدد المطلوب من المتغيرات المحلية. على سبيل المثال، إذا كانت هناك حاجة إلى تعويم محلي وطول محلي (إجمالي 12 بايت)، فيجب تقليل مؤشر المكدس بمقدار 12 لتوفير مساحة لهذه المتغيرات المحلية. في لغة عالية المستوى مثل C، هذا يعني الإعلان عن المتغيرات دون تعيين (تهيئة) القيم.

2. بعد ذلك، يجب حفظ قيم أي سجلات تم حفظها بواسطة المستدعي المعين (سجلات الأغراض العامة التي لم يحفظها المتصل) والتي تستخدمها الوظيفة. لحفظ السجلات، ادفعها إلى المكدس. السجلات المحفوظة للمستدعي هي RBX وRBP وR12 إلى R15 (يتم الاحتفاظ بـ RSP أيضًا بواسطة اصطلاح الاستدعاء، ولكن لا يلزم دفعها على المكدس أثناء هذه الخطوة).

بعد تنفيذ هذه الإجراءات الثلاثة، قد يستمر التشغيل الفعلي للروتين الفرعي. عندما يكون الروتين الفرعي جاهزًا للعودة، تستمر قواعد اصطلاح الاتصال.

3. عند الانتهاء من الروتين الفرعي، يجب وضع القيمة المرجعة للروتين الفرعي في RAX إذا لم تكن موجودة بالفعل.

4. يجب أن يستعيد الروتين الفرعي القيم القديمة لأية سجلات محفوظة للمستدعي (RBX، وRBP، وR12 إلى R15) التي تم تعديلها. تتم استعادة محتويات السجل عن طريق إخراجها من المكدس. لاحظ أنه يجب أن تظهر السجلات بالترتيب العكسي الذي تم دفعها به.

5. بعد ذلك، نقوم بإلغاء تخصيص المتغيرات المحلية. أسهل طريقة للقيام بذلك هي إضافة نفس المبلغ إلى RSP الذي تم طرحه منه في الخطوة 1.

6. أخيرًا، نعود إلى المتصل بتنفيذ أمر ret. ستقوم هذه التعليمات بالعثور على عنوان الإرجاع المناسب وإزالته من المكدس.

مثال على نص روتين فرعي للمتصل لاستدعاء روتين فرعي آخر وهو 'myFunc' هو كما يلي (اقرأ التعليقات):

; تريد استدعاء وظيفة 'myFunc' التي تستغرق ثلاثة

; المعلمة عدد صحيح. المعلمة الأولى في RAX .

; المعلمة الثانية هي الثابت 456. الثالثة

; المعلمة موجودة في موقع الذاكرة 'متغير'

دفع RDI ; سيكون rdi معلمًا، لذا احفظه

; طويل retVal = myFunc ( x , 456 , z ) ;

موف ردى , راكس ; وضع المعلمة الأولى في RDI

موف آر إس آي، 456؛ وضع المعلمة الثانية في مؤشر القوة النسبية

موف ردكس، [متغير]؛ وضع المعلمة الثالثة في RDX

اتصل بـ myFunc؛ استدعاء الوظيفة

البوب آر دي؛ استعادة قيمة RDI المحفوظة

; القيمة المرجعة لـ myFunc متاحة الآن في RAX

مثال على وظيفة المستدعي (myFunc) هو (اقرأ التعليقات):

myFunc :

; ∗∗∗ مقدمة روتينية قياسية ∗∗∗

فرعية آر إس بي، 8؛ مساحة لمتغير محلي (نتيجة) 64 بت باستخدام كود التشغيل 'الفرعي'.

دفع rbx ; حفظ المستدعي - حفظ السجلات

دفع ربب ; سيتم استخدام كلاهما بواسطة myFunc

; ∗∗∗ الجسم الروتيني الفرعي ∗∗∗

موف راكس، آر دي؛ المعلمة 1 إلى RAX

موف ربب، مؤشر القوة النسبية؛ المعلمة 2 إلى RBP

موف آر بي إكس، آر دي إكس؛ المعلمة 3 إلى rb x

موف [ RSP + 1 6 ] , rbx ; ضع rbx في المتغير المحلي

أضف [ rsp + 1 6 ] , rbp ; أضف rbp إلى المتغير المحلي

موف راكس , [ آر إس بي +16 ] ; نقل محتويات المتغير المحلي إلى RAX

; (قيمة الإرجاع/النتيجة النهائية)

; ∗∗∗ الخاتمة الروتينية القياسية ∗∗∗

البوب آر بي بي ; استعادة المستدعي حفظ السجلات

البوب آر بي إكس؛ عكس عندما دفعت

إضافة آر إس بي، 8؛ إلغاء تخصيص المتغير المحلي (المتغيرات). 8 يعني 8 بايت

متقاعد ; قم بإخراج القيمة العليا من المكدس، واقفز هناك

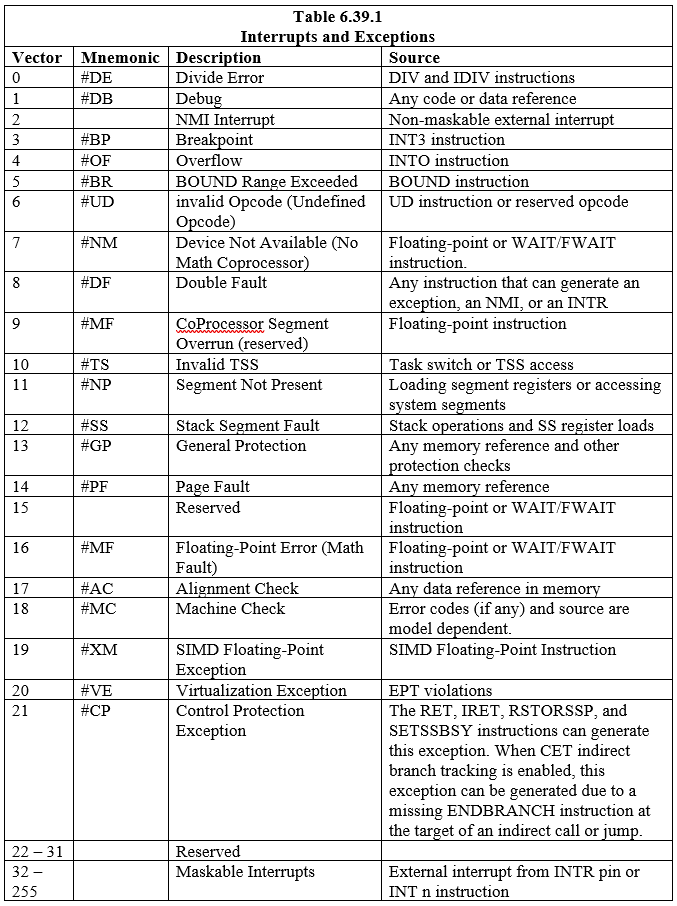

6.39 المقاطعات والاستثناءات لـ x64

يوفر المعالج آليتين لمقاطعة تنفيذ البرنامج والمقاطعات والاستثناءات:

- المقاطعة هي حدث غير متزامن (يمكن أن يحدث في أي وقت) يتم تشغيله عادةً بواسطة جهاز الإدخال/الإخراج.

- الاستثناء هو حدث متزامن (يحدث عند تنفيذ التعليمات البرمجية، أو برمجتها مسبقًا، بناءً على بعض الأحداث) التي يتم إنشاؤها عندما يكتشف المعالج واحدًا أو أكثر من الشروط المحددة مسبقًا أثناء تنفيذ التعليمات. يتم تحديد ثلاث فئات من الاستثناءات: الأخطاء، والفخاخ، والإحباط.

يستجيب المعالج للمقاطعات والاستثناءات بنفس الطريقة بشكل أساسي. عند الإشارة إلى مقاطعة أو استثناء، يوقف المعالج تنفيذ البرنامج أو المهمة الحالية ويتحول إلى إجراء معالج مكتوب خصيصًا للتعامل مع حالة المقاطعة أو الاستثناء. يصل المعالج إلى إجراء المعالج من خلال إدخال في جدول واصف المقاطعة (IDT). عندما يكمل المعالج معالجة المقاطعة أو الاستثناء، يتم إرجاع التحكم في البرنامج إلى البرنامج أو المهمة التي تمت مقاطعتها.

عادةً ما يتعامل نظام التشغيل و/أو برامج التشغيل التنفيذية و/أو الأجهزة مع المقاطعات والاستثناءات بشكل مستقل عن برامج التطبيق أو المهام. ومع ذلك، يمكن للبرامج التطبيقية الوصول إلى معالجات المقاطعة والاستثناءات المدمجة في نظام التشغيل أو تنفيذها من خلال استدعاءات لغة التجميع.

تم تعريف ثمانية عشر (18) مقاطعة واستثناءات محددة مسبقًا، والتي ترتبط بالإدخالات في IDT. يمكن أيضًا إنشاء مائتين وأربعة وعشرين (224) مقاطعة محددة من قبل المستخدم وربطها بالجدول. يتم تعريف كل مقاطعة واستثناء في IDT برقم يسمى 'المتجه'. يسرد الجدول 6.39.1 المقاطعات والاستثناءات مع الإدخالات في IDT والمتجهات الخاصة بها. المتجهات من 0 إلى 8، ومن 10 إلى 14، ومن 16 إلى 19 هي المقاطعات والاستثناءات المحددة مسبقًا. المتجهات من 32 إلى 255 مخصصة للمقاطعات المعرفة بواسطة البرنامج (المستخدم) والتي تكون إما لمقاطعات البرامج أو مقاطعات الأجهزة القابلة للإخفاء.

عندما يكتشف المعالج مقاطعة أو استثناء، فإنه يقوم بأحد الأمور التالية:

- تنفيذ استدعاء ضمني لإجراء معالج

- تنفيذ استدعاء ضمني لمهمة معالج

6.4 أساسيات هندسة الكمبيوتر ARM 64 بت

تحدد بنيات ARM عائلة من معالجات RISC المناسبة للاستخدام في مجموعة واسعة من التطبيقات. ARM عبارة عن بنية تحميل/تخزين تتطلب تحميل البيانات من الذاكرة إلى السجل قبل إجراء أي معالجة مثل عملية ALU (وحدة المنطق الحسابي). تعليمات لاحقة تخزن النتيجة مرة أخرى في الذاكرة. في حين أن هذا قد يبدو بمثابة خطوة إلى الوراء من بنيات x86 وx64، التي تعمل مباشرة على المعاملات في الذاكرة في تعليمات واحدة (باستخدام سجلات المعالج، بالطبع)، فإن نهج التحميل/التخزين، في الممارسة العملية، يسمح بعدة عمليات متسلسلة ليتم تنفيذها بسرعة عالية على المعامل بمجرد تحميله في أحد سجلات المعالج العديدة. تتمتع معالجات ARM بخيار endianness الصغير أو endianness الكبير. الإعداد الافتراضي لـ ARM 64 هو الإعداد الصغير وهو التكوين الذي تستخدمه أنظمة التشغيل بشكل شائع. تعتبر بنية ARM 64 بت حديثة وتم إعدادها لتحل محل بنية ARM 32 بت.

ملحوظة : يبلغ طول كل تعليمات لـ ARM μP 64 بت 4 بايت (32 بت).

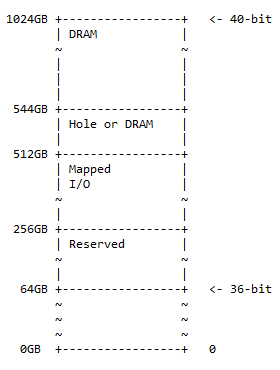

6.41 مجموعة تسجيل ARM 64 بت

يوجد 31 سجلًا للأغراض العامة 64 بت لـ 64 بت ARM μP. ويوضح الرسم البياني التالي سجلات الأغراض العامة وبعض السجلات المهمة:

الشكل 4.11.1 64 بت للأغراض العامة وبعض السجلات المهمة

يُشار إلى سجلات الأغراض العامة باسم X0 وحتى X30. تتم الإشارة إلى الجزء الأول 32 بت لكل سجل باسم W0 حتى W30. عندما لا يتم التركيز على الفرق بين 32 بت و64 بت، يتم استخدام البادئة 'R'. على سبيل المثال، يشير R14 إلى W14 أو X14.

يحتوي الطراز 6502 μP على عداد برامج 16 بت ويمكنه معالجة 2 16 مواقع بايت الذاكرة. يحتوي ARM μP 64 بت على عداد برامج 64 بت ويمكنه معالجة ما يصل إلى 2 64 = 1.844674407 × 1019 (في الواقع 18,446,744,073,709,551,616) مواقع بايت الذاكرة. يحتفظ عداد البرنامج بعنوان التعليمة التالية التي سيتم تنفيذها. يبلغ طول تعليمات ARM64 أو AArch64 عادةً أربعة بايت. يقوم المعالج تلقائيًا بزيادة هذا السجل بمقدار أربعة بعد جلب كل تعليمات من الذاكرة.

سجل Stack Pointer أو SP ليس من بين 31 سجلاً للأغراض العامة. يشير مؤشر المكدس لأي بنية إلى آخر إدخال للمكدس في الذاكرة. بالنسبة لـ ARM-64، تنمو المكدس للأسفل.

يحتوي 6502 μP على سجل حالة المعالج 8 بت. يسمى المعادل في ARM64 سجل PSTATE. يقوم هذا السجل بتخزين العلامات المستخدمة لنتائج العمليات وللتحكم في المعالج (μP). يبلغ عرضه 32 بت. يوفر الجدول التالي الأسماء والفهرس والمعاني للبتات شائعة الاستخدام في سجل PSTATE:

| الجدول 6.41.1 أعلام PSTATE الأكثر استخدامًا (بت) |

||

|---|---|---|

| رمز | قليل | غاية |

| م | 0-3 | الوضع: مستوى امتياز التنفيذ الحالي (USR، SVC، وما إلى ذلك). |

| ت | 4 | الإبهام: يتم ضبطه إذا كانت مجموعة تعليمات T32 (الإبهام) نشطة. إذا كان واضحًا، فإن مجموعة تعليمات ARM نشطة. يمكن لرمز المستخدم ضبط هذا الشيء ومسحه. |

| و | 9 | Endianness: يؤدي تعيين هذا البت إلى تمكين وضع النهاية الكبيرة. إذا كان واضحًا، يكون وضع النهاية الصغيرة نشطًا. الافتراضي هو وضع endian الصغير. |

| س | 27 | علامة التشبع التراكمي: يتم تعيينها في حالة حدوث تجاوز أو تشبع في مرحلة ما من سلسلة من العمليات |

| في | 28 | علامة التجاوز: يتم تعيينها إذا أدت العملية إلى تجاوز السعة الموقعة. |

| ج | 29 | علامة الحمل: تشير إلى ما إذا كان الجمع ينتج حملاً أم أن الطرح ينتج استعارة. |

| مع | 30 | علامة الصفر: يتم تعيينها إذا كانت نتيجة العملية صفراً. |

| ن | 31 | العلم السلبي: يتم تعيينه إذا كانت نتيجة العملية سلبية. |

يحتوي ARM-64 μP على العديد من السجلات الأخرى.

SIMD

يعنيSIMD تعليمات واحدة وبيانات متعددة. وهذا يعني أن تعليمات لغة التجميع الواحدة يمكن أن تعمل على بيانات متعددة في نفس الوقت في معالج دقيق واحد. هناك اثنان وثلاثون سجلاً بعرض 128 بت للاستخدام مع عمليات SIMD والفاصلة العائمة.

6.42 رسم خرائط الذاكرة

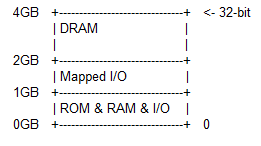

ذاكرة الوصول العشوائي (RAM) وذاكرة الوصول العشوائي (DRAM) كلاهما من ذكريات الوصول العشوائي. DRAM أبطأ في التشغيل من ذاكرة الوصول العشوائي. DRAM أرخص من ذاكرة الوصول العشوائي. إذا كان هناك أكثر من 32 جيجابايت من ذاكرة DRAM المستمرة في الذاكرة، فسيكون هناك المزيد من مشكلات إدارة الذاكرة: 32 جيجابايت = 32 × 1024 × 1024 × 1024 بايت. بالنسبة لمساحة ذاكرة كاملة أكبر بكثير من 32 جيجابايت، يجب أن تتخلل ذاكرة الوصول العشوائي الديناميكية (DRAM) التي تزيد عن 32 جيجابايت مع ذاكرة الوصول العشوائي (RAM) لإدارة الذاكرة بشكل أفضل. من أجل فهم خريطة الذاكرة ARM-64، يجب عليك أولاً فهم خريطة الذاكرة سعة 4 جيجابايت لوحدة المعالجة المركزية ARM 32 بت (CPU). وحدة المعالجة المركزية تعني μP. بالنسبة لجهاز كمبيوتر 32 بت، الحد الأقصى لمساحة الذاكرة القابلة للعنونة هو 2 32 = 4 × 2 10 × 2 10 × 2 10 = 4 × 1024 × 1024 × 1024 = 4,294,967,296 = 4 جيجابايت.

خريطة ذاكرة ARM 32 بت

خريطة الذاكرة لـ ARM 32 بت هي:

بالنسبة لجهاز كمبيوتر 32 بت، الحد الأقصى لحجم الذاكرة بأكملها هو 4 جيجابايت. من عنوان 0 جيجابايت إلى عنوان 1 جيجابايت يوجد نظام تشغيل ROM وذاكرة الوصول العشوائي ومواقع الإدخال/الإخراج. الفكرة الكاملة لنظام التشغيل ROM، وذاكرة الوصول العشوائي، وعناوين الإدخال/الإخراج مشابهة لحالة Commodore-64 مع وحدة المعالجة المركزية 6502 المحتملة. يوجد نظام التشغيل ROM الخاص بـ Commodore-64 في الجزء العلوي من مساحة الذاكرة. نظام التشغيل ROM هنا أكبر بكثير من نظام Commodore-64، وهو موجود في بداية مساحة عنوان الذاكرة بأكملها. عند مقارنته بأجهزة الكمبيوتر الحديثة الأخرى، فإن نظام التشغيل ROM هنا مكتمل، بمعنى أنه يمكن مقارنته بكمية نظام التشغيل الموجودة في محركات الأقراص الثابتة الخاصة بها. هناك سببان رئيسيان لوجود نظام التشغيل في دوائر ROM المتكاملة: 1) تُستخدم وحدات المعالجة المركزية ARM في الغالب في الأجهزة الصغيرة مثل الهواتف الذكية. العديد من محركات الأقراص الثابتة أكبر حجمًا من الهواتف الذكية والأجهزة الصغيرة الأخرى، 2) للأمان. عندما يكون نظام التشغيل في ذاكرة القراءة فقط، لا يمكن إتلافه (الكتابة فوق الأجزاء) بواسطة المتسللين. تعد أقسام ذاكرة الوصول العشوائي (RAM) وأقسام الإدخال / الإخراج أيضًا كبيرة جدًا مقارنة بأقسام Commodore-64.

عند توصيل الطاقة بنظام تشغيل ROM 32 بت، يجب أن يبدأ نظام التشغيل عند (التمهيد من) عنوان 0x00000000 أو عنوان 0xFFFF0000 إذا تم تمكين HiVECs. لذا، عند توصيل الطاقة بعد مرحلة إعادة التعيين، يقوم جهاز وحدة المعالجة المركزية بتحميل 0x00000000 أو 0xFFFF0000 إلى عداد البرامج. البادئة '0x' تعني النظام الست عشري. عنوان التمهيد لوحدات المعالجة المركزية ARMv8 64 بت هو تطبيق محدد. ومع ذلك، ينصح المؤلف مهندس الكمبيوتر بالبدء عند 0x00000000 أو 0xFFFF0000 من أجل التوافق مع الإصدارات السابقة.

من 1 جيجابايت إلى 2 جيجابايت هو الإدخال/الإخراج المعين. يوجد فرق بين الإدخال/الإخراج المعين والإدخال/الإخراج فقط الموجود بين 0 جيجابايت و1 جيجابايت. مع الإدخال/الإخراج، يتم إصلاح عنوان كل منفذ كما هو الحال مع Commodore-64. مع عمليات الإدخال/الإخراج المعينة، ليس بالضرورة أن يكون عنوان كل منفذ هو نفسه لكل عملية يقوم بها الكمبيوتر (ديناميكي).

من 2 جيجا بايت إلى 4 جيجا بايت هو DRAM. هذه هي ذاكرة الوصول العشوائي المتوقعة (أو المعتادة). يشير DRAM إلى Dynamic RAM، وليس بمعنى تغيير العنوان أثناء تشغيل الكمبيوتر ولكن بمعنى أن قيمة كل خلية في ذاكرة الوصول العشوائي الفعلية يجب تحديثها عند كل نبضة على مدار الساعة.

ملحوظة :

- من 0x0000,0000 إلى 0x0000، FFFF هو نظام التشغيل ROM.

- من 0x0001,0000 إلى 0x3FFF، FFFF، يمكن أن يكون هناك المزيد من ROM، ثم RAM، ثم بعض الإدخال/الإخراج.

- من 0x4000,0000 إلى 0x7FFF، FFFF، يُسمح بإدخال/إخراج إضافي و/أو إدخال/إخراج معين.

- من 0x8000,0000 إلى 0xFFFF، FFFF هو DRAM المتوقع.

وهذا يعني أن ذاكرة الوصول العشوائي الديناميكية (DRAM) المتوقعة ليس من الضروري أن تبدأ عند حدود الذاكرة البالغة 2 جيجابايت، عمليًا. لماذا يجب على المبرمج أن يحترم الحدود المثالية عندما لا يكون هناك ما يكفي من بنوك ذاكرة الوصول العشوائي الفعلية المثبتة على اللوحة الأم؟ وذلك لأن العميل ليس لديه ما يكفي من المال لجميع بنوك RAM.

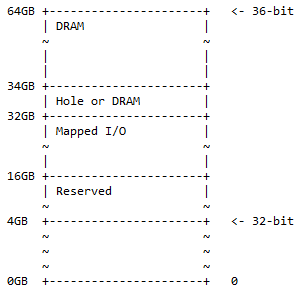

خريطة ذاكرة ARM 36 بت

بالنسبة لجهاز كمبيوتر ARM 64 بت، يتم استخدام جميع الـ 32 بت لمعالجة الذاكرة بأكملها. بالنسبة لكمبيوتر ARM 64 بت، يمكن استخدام أول 36 بت لمعالجة الذاكرة بأكملها والتي، في هذه الحالة، 2 36 = 68,719,476,736 = 64 جيجابايت. هذا كثير من الذاكرة بالفعل. أجهزة الكمبيوتر العادية اليوم لا تحتاج إلى هذا القدر من الذاكرة. هذا لم يصل بعد إلى الحد الأقصى لنطاق الذاكرة الذي يمكن الوصول إليه بواسطة 64 بت. خريطة الذاكرة لـ 36 بت لوحدة المعالجة المركزية ARM هي:

من عنوان 0 جيجابايت إلى عنوان 4 جيجابايت توجد خريطة ذاكرة 32 بت. 'محجوز' يعني عدم استخدامه ويتم الاحتفاظ به للاستخدام المستقبلي. ليس من الضروري أن تكون بنوك الذاكرة الفعلية مثبتة على اللوحة الأم لتلك المساحة. هنا، DRAM والإدخال/الإخراج المعين لهما نفس المعاني كما في خريطة الذاكرة 32 بت.

يمكن العثور على الموقف التالي في الممارسة العملية:

- 0x1 0000 0000 – 0x3 FFFF FFFF; محجوز. تم حجز 12 جيجابايت من مساحة العنوان للاستخدام المستقبلي.

- 0x4 0000 0000 - 0x7 FFFF FFFF؛ المعينة الإدخال/الإخراج. تتوفر مساحة عنوان تبلغ 16 جيجابايت لعمليات الإدخال/الإخراج المعينة ديناميكيًا.

- 0x8 0000 0000 – 0x8 7FFF FFFF FFFF; ثقب أو DRAM. يمكن أن تحتوي مساحة العنوان البالغة 2 جيجابايت على أي مما يلي:

- فتحة لتمكين تقسيم جهاز DRAM (كما هو موضح في المناقشة التالية).

- درهم.

- 0x8 8000 0000 – 0xF FFFF FFFF; درهم. 30 جيجابايت من مساحة العنوان لـ DRAM.

خريطة الذاكرة هذه عبارة عن مجموعة شاملة من خريطة العناوين 32 بت، مع تقسيم المساحة الإضافية إلى 50% DRAM (1/2) مع فتحة اختيارية فيها و25% من مساحة الإدخال/الإخراج المعينة ومساحة محجوزة (1/4) ). النسبة المتبقية 25% (1/4) مخصصة لخريطة الذاكرة 32 بت ½ + ¼ + ¼ = 1.

ملحوظة : من 32 بت إلى 360 بت هو إضافة 4 بت إلى الجانب الأكثر أهمية وهو 36 بت.

خريطة الذاكرة 40 بت

خريطة العناوين 40 بت هي مجموعة شاملة من خريطة العناوين 36 بت وتتبع نفس النمط المتمثل في 50% DRAM من فتحة اختيارية فيها، و25% من مساحة الإدخال/الإخراج المعينة والمساحة المحجوزة، والباقي 25% مساحة لخريطة الذاكرة السابقة (36 بت). الرسم التخطيطي لخريطة الذاكرة هو:

حجم الثقب 544 – 512 = 32 جيجابايت. يمكن العثور على الموقف التالي في الممارسة العملية:

- 0x10 0000 0000 – 0x3F FFFF FFFF; محجوز. تم حجز 192 جيجابايت من مساحة العنوان للاستخدام المستقبلي.

- 0x40 0000 0000 - 0x7F FFFF FFFF؛ تم تعيينها. تتوفر مساحة عنوان تبلغ 256 جيجابايت للإدخال/الإخراج للإدخال/الإخراج المعين ديناميكيًا.

- 0x80 0000 0000 – 0x87 FFFF FFFF; ثقب أو DRAM. يمكن أن تحتوي مساحة العنوان البالغة 32 جيجابايت على أي مما يلي:

- فتحة لتمكين تقسيم جهاز DRAM (كما هو موضح في المناقشة التالية)

- درهم

- 0x88 0000 0000 - 0xFF FFFF FFFF؛ درهم. 480 جيجابايت من مساحة العنوان لـ DRAM.

ملحوظة : من 36 بت إلى 40 بت هو إضافة 4 بت إلى الجانب الأكثر أهمية وهو 36 بت.

ثقب الرام

في خريطة الذاكرة التي تتجاوز 32 بت، تكون إما فتحة DRAM أو استمرارًا لـ DRAM من الأعلى. عندما تكون فتحة، يجب تقديرها على النحو التالي: توفر فتحة DRAM طريقة لتقسيم جهاز DRAM كبير إلى نطاقات عناوين متعددة. يتم اقتراح فتحة DRAM الاختيارية في بداية الحد الأعلى لعنوان DRAM. يتيح ذلك نظامًا مبسطًا لفك التشفير عند تقسيم جهاز DRAM ذو سعة كبيرة عبر المنطقة السفلية الموجهة فعليًا.

على سبيل المثال، يتم تقسيم جزء DRAM سعة 64 جيجابايت إلى ثلاث مناطق مع إزاحة العنوان التي يتم إجراؤها عن طريق طرح بسيط في بتات العنوان ذات الترتيب العالي كما يلي:

| الجدول 6.42.1 مثال على تقسيم ذاكرة الوصول العشوائي الديناميكية (DRAM) سعة 64 جيجابايت مع وجود ثقوب |

|||

|---|---|---|---|

| العناوين الفعلية في شركة نفط الجنوب | عوض | عنوان DRAM الداخلي | |

| 2 جيجابايت (خريطة 32 بت) | 0x00 8000 0000 – 0x00 FFFF FFFF | -0x00 8000 0000 | 0x00 0000 0000 – 0x00 7FFF FFFF |

| 30 جيجابايت (خريطة 36 بت) | 0x08 8000 0000 – 0x0F FFFF FFFF | -0x08 0000 0000 | 0x00 8000 0000 – 0x07 FFFF FFFF |

| 32 جيجابايت (خريطة 40 بت) | 0x88 0000 0000 – 0x8F FFFF FFFF | -0x80 0000 0000 | 0x08 0000 0000 – 0x0F FFFF FFFF |

خرائط الذاكرة الموجهة 44 بت و48 بت المقترحة لوحدات المعالجة المركزية ARM

افترض أن الكمبيوتر الشخصي يحتوي على ذاكرة تبلغ سعتها 1024 جيجابايت (= 1 تيرابايت)؛ وهذا هو الكثير من الذاكرة. وهكذا، فإن خرائط الذاكرة الموجهة 44 بت و48 بت لوحدات المعالجة المركزية ARM بسعة 16 تيرابايت و256 تيرابايت، على التوالي، هي مجرد مقترحات لاحتياجات الكمبيوتر المستقبلية. في الواقع، تتبع هذه المقترحات الخاصة بوحدات المعالجة المركزية ARM نفس تقسيم الذاكرة حسب النسبة مثل خرائط الذاكرة السابقة. أي: 50% من ذاكرة الوصول العشوائي الديناميكي (DRAM) مع وجود ثقب اختياري فيها، و25% من مساحة الإدخال/الإخراج المعينة والمساحة المحجوزة، وباقي مساحة 25% لخريطة الذاكرة السابقة.

لا يزال من المقرر اقتراح خرائط الذاكرة الموجهة 52 بت و56 بت و60 بت و64 بت لـ ARM 64 بت في المستقبل البعيد. وإذا كان العلماء في ذلك الوقت ما زالوا يجدون أن تقسيم مساحة الذاكرة بأكملها بنسبة 50:25:25 مفيد، فسوف يحافظون على النسبة.

ملحوظة : يشير SoC إلى System-on-Chip الذي يشير إلى الدوائر الموجودة في شريحة μP والتي لم تكن موجودة لولا ذلك.

SRAM أو ذاكرة الوصول العشوائي الثابتة هي أسرع من ذاكرة DRAM التقليدية، ولكنها تتطلب مساحة أكبر من السيليكون. SRAM لا يتطلب التحديث. يمكن للقارئ أن يتخيل ذاكرة الوصول العشوائي (RAM) على أنها SRAM.

6.43 أوضاع معالجة لغة التجميع لـ ARM 64

ARM عبارة عن بنية تحميل/تخزين تتطلب تحميل البيانات من الذاكرة إلى سجل المعالج قبل إجراء أي معالجة مثل عملية المنطق الحسابي معها. تعليمات لاحقة تخزن النتيجة مرة أخرى في الذاكرة. في حين أن هذا قد يبدو بمثابة خطوة إلى الوراء من x86 وبنيات x64 اللاحقة، والتي تعمل مباشرة على المعاملات في الذاكرة في تعليمات واحدة، في الممارسة العملية، يسمح نهج التحميل/التخزين بتنفيذ العديد من العمليات المتسلسلة بسرعة عالية على معامل بمجرد تحميله في أحد سجلات المعالجات العديدة.

يحتوي تنسيق لغة التجميع ARM على أوجه تشابه واختلاف مع سلسلة x64 (x86).

- عوض : يمكن إضافة ثابت موقّع إلى السجل الأساسي. تتم كتابة الإزاحة كجزء من التعليمات. على سبيل المثال: يقوم ldr x0, [rx, #10] بتحميل r0 بالكلمة الموجودة في عنوان r1+10.

- يسجل : يمكن إضافة الزيادة غير الموقعة المخزنة في السجل إلى القيمة الموجودة في السجل الأساسي أو طرحها منها. على سبيل المثال: يقوم ldr r0, [x1, x2] بتحميل r0 بالكلمة الموجودة في العنوان x1+x2. يمكن اعتبار أي من السجلات بمثابة السجل الأساسي.

- سجل متدرج : يتم إزاحة الزيادة في السجل إلى اليسار أو اليمين بواسطة عدد محدد من مواضع البت قبل إضافتها إلى قيمة السجل الأساسية أو طرحها منها. على سبيل المثال: يقوم ldr x0, [x1, x2, lsl #3] بتحميل r0 بالكلمة الموجودة في عنوان r1+(r2×8). يمكن أن يكون الإزاحة إزاحة منطقية لليسار أو اليمين (lsl أو lsr) والتي تُدرج بتات صفرية في مواضع البتات الفارغة أو إزاحة حسابية لليمين (asr) تعمل على تكرار بت الإشارة في المواضع الفارغة.

عندما يتعلق الأمر بمعاملين، تأتي الوجهة قبل المصدر (على اليسار) (هناك بعض الاستثناءات لهذا). رموز التشغيل الخاصة بلغة تجميع ARM غير حساسة لحالة الأحرف.

وضع معالجة ARM64 الفوري

مثال:

موف r0, #0xFF000000 ; قم بتحميل القيمة 32 بت FF000000h إلى r0

القيمة العشرية لا تحتوي على 0x ولكنها لا تزال مسبوقة بـ #.

سجل مباشر

مثال:

الحركة X0، X1؛ انسخ x1 إلى x0

سجل بشكل غير مباشر

مثال:

شارع X0، [X3]؛ قم بتخزين x0 على العنوان الموجود في x3

تسجيل غير مباشر مع الأوفست

أمثلة:

لدر X0، [x1، #32] ; قم بتحميل r0 بالقيمة الموجودة على العنوان [r1+32]؛ r1 هو السجل الأساسي

شارع X0، [X1، #4] ; قم بتخزين r0 على العنوان [r1+4]؛ r1 هو السجل الأساسي؛ الأرقام هي أساس 10

تسجيل غير مباشر مع الإزاحة (متزايد مسبقًا)

أمثلة:

LDR X0، [X1، #32]! ; قم بتحميل r0 بـ [r1+32] وقم بتحديث r1 إلى (r1+32)

شارع x0، [x1، #4]! ; قم بتخزين r0 إلى [r1+4] وتحديث r1 إلى (r1+4)

لاحظ استخدام '!' رمز.

التسجيل غير المباشر مع الإزاحة (الزيادة اللاحقة)

أمثلة:

لدر X0، [x1]، #32؛ قم بتحميل [x1] إلى x0، ثم قم بتحديث x1 إلى (x1+32)

شارع x0، [x1]، #4؛ قم بتخزين x0 إلى [x1]، ثم قم بتحديث x1 إلى (x1+4)

تسجيل مزدوج غير مباشر

عنوان المعامل هو مجموع السجل الأساسي وسجل الزيادة. أسماء السجلات محاطة بأقواس مربعة.

أمثلة:

لدر x0، [x1، x2] ؛ تحميل x0 مع [x1+x2]

شارع X0، [RX، X2]؛ قم بتخزين x0 إلى [x1+x2]

وضع العنونة النسبية

في وضع العنونة النسبي، تكون التعليمات الفعالة هي التعليمات التالية في عداد البرامج، بالإضافة إلى فهرس. يمكن أن يكون المؤشر إيجابيا أو سلبيا.

مثال:

لدر X0، [كمبيوتر شخصي، رقم 24]

وهذا يعني تسجيل التحميل X0 بالكلمة التي يشير إليها محتوى الكمبيوتر بالإضافة إلى 24.

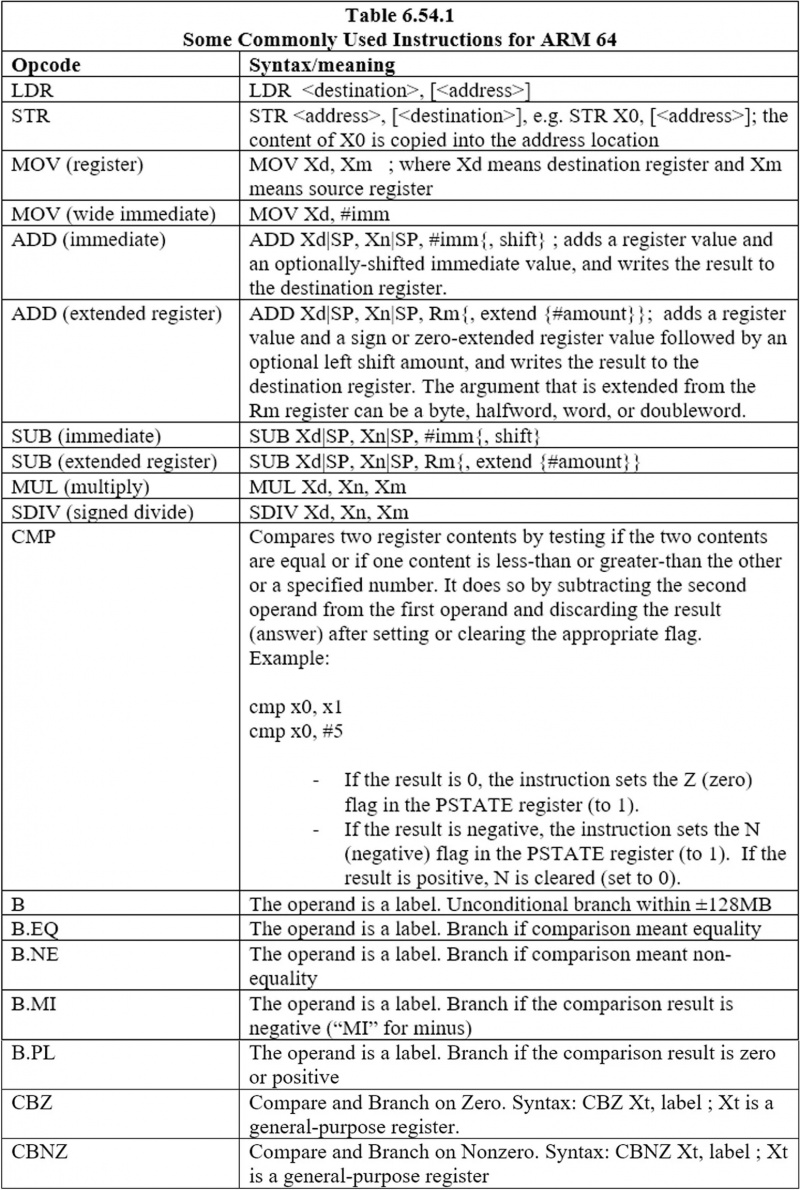

6.44 بعض التعليمات الشائعة الاستخدام لـ ARM 64

فيما يلي التعليمات الشائعة الاستخدام:

6.45 حلقات

توضيح

يستمر التعليمة البرمجية التالية في إضافة القيمة الموجودة في سجل X10 إلى القيمة الموجودة في X9 حتى تصبح القيمة الموجودة في X8 صفرًا. افترض أن جميع القيم هي أعداد صحيحة. يتم طرح القيمة في X8 بمقدار 1 في كل تكرار:

حلقة:

CBZ X8، تخطي

إضافة X9، X9، X10؛ X9 الأول هو الوجهة والثاني X9 هو المصدر

فرعي X8، X8، #1؛ X8 الأول هو الوجهة والثاني X8 هو المصدر

حلقة B

يتخطى:

كما هو الحال مع 6502 μP وX64 μP، تبدأ التسمية في ARM 64 μP في بداية السطر. تبدأ بقية التعليمات في بعض المسافات بعد بداية السطر. مع x64 وARM 64، تكون التسمية متبوعة بنقطتين وسطر جديد. بينما في 6502، التسمية متبوعة بتعليمات بعد مسافة. في الكود السابق، تعني التعليمات الأولى وهي 'CBZ X8،تخطي' أنه إذا كانت القيمة في X8 صفرًا، فاستمر عند علامة 'تخطي:'، مع تخطي التعليمات الموجودة بينهما والاستمرار في بقية التعليمات أدناه 'يتخطى:'. 'الحلقة B' هي قفزة غير مشروطة إلى تسمية 'الحلقة'. يمكن استخدام أي اسم تسمية آخر بدلاً من 'الحلقة'.

لذلك، كما هو الحال مع 6502 μP، استخدم تعليمات الفرع للحصول على حلقة مع ARM 64.

6.46 ARM 64 الإدخال/الإخراج

يتم تعيين الذاكرة لجميع أجهزة ARM الطرفية (المنافذ الداخلية). وهذا يعني أن واجهة البرمجة عبارة عن مجموعة من السجلات الموجهة للذاكرة (المنافذ الداخلية). عنوان هذا السجل هو إزاحة من عنوان قاعدة ذاكرة محدد. وهذا مشابه لكيفية قيام 6502 بالإدخال/الإخراج. لا يحتوي ARM على خيار مساحة عنوان الإدخال/الإخراج المنفصلة.

6.47 كومة من ARM 64

يحتوي ARM 64 على مكدس في الذاكرة (RAM) بطريقة مشابهة لتلك الموجودة في 6502 وx64. ومع ذلك، مع ARM64، لا يوجد رمز تشغيل دفع أو فرقع. المكدس في ARM 64 ينمو أيضًا للأسفل. يشير العنوان الموجود في مؤشر المكدس مباشرة بعد البايت الأخير من القيمة الأخيرة التي تم وضعها في المكدس.

السبب وراء عدم وجود كود تشغيل منبثق أو دفعي عام لـ ARM64 هو أن ARM 64 يدير مكدسه في مجموعات مكونة من 16 بايت متتالية. ومع ذلك، توجد القيم في مجموعات بايت مكونة من بايت واحد وبايتين وأربعة بايت و8 بايت. لذلك، يمكن وضع قيمة واحدة في المكدس، ويتم ملء بقية الأماكن (مواقع البايت) لتعويض 16 بايت بالبايتات الوهمية. وهذا له عيب إضاعة الذاكرة. الحل الأفضل هو ملء الموقع المكون من 16 بايت بقيم أصغر والحصول على بعض التعليمات البرمجية المكتوبة للمبرمج والتي تتعقب مصدر القيم الموجودة في الموقع المكون من 16 بايت (التسجيلات). هذا الرمز الإضافي مطلوب أيضًا عند سحب القيم. البديل لذلك هو ملء سجلين للأغراض العامة سعة كل منهما 8 بايت بقيم مختلفة، ثم إرسال محتويات السجلين سعة 8 بايت إلى المكدس. لا تزال هناك حاجة إلى رمز إضافي هنا لتتبع القيم الصغيرة المحددة التي تدخل المكدس وتترك المكدس.

يقوم الكود التالي بتخزين أربع بيانات بحجم 4 بايت في المكدس:

شارع W0، [SP، #-4]!

شارع W1، [SP، #-8]!

شارع W2، [SP، #-12]!

شارع W3، [SP، #-16]!

يتم إرسال البايتات الأربع الأولى (w) من السجلات – x0 وx1 وx2 وx3 – إلى مواقع 16 بايت متتالية في المكدس. لاحظ استخدام 'str' وليس 'دفع'. لاحظ علامة التعجب في نهاية كل تعليمة. نظرًا لأن مكدس الذاكرة ينمو للأسفل، فإن القيمة الأولى المكونة من أربعة بايت تبدأ عند موضع يقل بمقدار أربعة بايت عن موضع مؤشر المكدس السابق. تتبع بقية القيم ذات الأربع بايتات، وتنخفض. سيقوم مقطع التعليمات البرمجية التالي بعمل المكافئ الصحيح (والمرتب) لظهور البايتات الأربعة:

لدر w3، [س]، #0

لدر w2، [س]، #4

لدر w1، [س]، #8

لدر w0، [س]، #12

لاحظ استخدام كود التشغيل ldr بدلاً من pop. لاحظ أيضًا أن رمز التعجب غير مستخدم هنا.

يمكن إرسال كافة البايتات الموجودة في X0 (8 بايت) وX1 (8 بايت) إلى موقع 16 بايت في المكدس كما يلي:

stp x0, x1, [sp, #-16]! ; 8 + 8 = 16

في هذه الحالة، ليست هناك حاجة إلى سجلات x2 (w2) وx3 (w3). كافة البايتات المطلوبة موجودة في سجلات X0 وX2. لاحظ كود التشغيل stp لتخزين أزواج محتويات التسجيل في ذاكرة الوصول العشوائي (RAM). لاحظ أيضًا رمز التعجب. ما يعادل البوب هو:

ldp x0, x1, [sp], #0

لا توجد علامة تعجب لهذه التعليمات. لاحظ رمز التشغيل LDP بدلاً من LDR لتحميل موقعين متتاليين للبيانات من الذاكرة إلى سجلين μP. تذكر أيضًا أن النسخ من الذاكرة إلى سجل μP يعد بمثابة تحميل، ويجب عدم الخلط بينه وبين تحميل ملف من القرص إلى ذاكرة الوصول العشوائي (RAM)، والنسخ من سجل μP إلى ذاكرة الوصول العشوائي (RAM) هو تخزين.

6.48 روتين فرعي

الروتين الفرعي عبارة عن كتلة من التعليمات البرمجية التي تؤدي مهمة، بناءً على بعض الوسائط بشكل اختياري وتقوم بإرجاع نتيجة اختياريًا. وفقًا للاتفاقية، يتم استخدام سجلات R0 إلى R3 (أربعة سجلات) لتمرير الوسيطات (المعلمات) إلى روتين فرعي، ويتم استخدام R0 لتمرير النتيجة مرة أخرى إلى المتصل. يستخدم الروتين الفرعي الذي يحتاج إلى أكثر من 4 مدخلات المكدس للمدخلات الإضافية. لاستدعاء روتين فرعي، استخدم الارتباط أو تعليمات الفرع الشرطي. بناء جملة تعليمات الارتباط هو:

تسمية BL

حيث BL هو كود التشغيل والتسمية تمثل بداية (عنوان) الروتين الفرعي. هذا الفرع غير مشروط، للأمام أو للخلف في حدود 128 ميجابايت. بناء جملة تعليمات الفرع الشرطي هو:

ب. تسمية كوند

حيث يكون الشرط هو الشرط، على سبيل المثال، eq (يساوي) أو ne (غير متساوي). يحتوي البرنامج التالي على روتين doadd الذي يضيف قيم وسيطتين ويعيد نتيجة في R0:

المنطقة الفرعية، الكود، للقراءة فقط؛ قم بتسمية هذه الكتلة من التعليمات البرمجية

دخول ; ضع علامة على التعليمات الأولى للتنفيذ

ابدأ تشغيل MOV r0, #10 ; إعداد المعلمات

موف آر 1، #3

بي إل دود ; استدعاء الروتين الفرعي

إيقاف MOV r0، #0x18 ؛ angel_SWIreason_ReportException

LDR r1, =0x20026 ; ADP_Stopped_ApplicationExit

إس في سي #0x123456؛ استضافة ARM شبه (SWI سابقًا)

doadd إضافة r0, r0, r1 ; رمز الروتين الفرعي

بي اكس لير ; العودة من الروتين الفرعي

;

نهاية ؛ وضع علامة على نهاية الملف

الأرقام المراد إضافتها هي العلامة العشرية 10 والعلامة العشرية 3. سيتم شرح أول سطرين في كتلة التعليمات البرمجية (البرنامج) هذه لاحقًا. ترسل الأسطر الثلاثة التالية 10 إلى سجل R0 و3 إلى سجل R1، وتستدعي أيضًا الروتين الفرعي doadd. 'doadd' هو الملصق الذي يحمل عنوان بداية الروتين الفرعي.

يتكون الروتين الفرعي من سطرين فقط. يضيف السطر الأول المحتوى 3 من R إلى المحتوى 10 من R0 مما يسمح بنتيجة 13 في R0. يعود السطر الثاني الذي يحتوي على كود تشغيل BX ومعامل LR من الروتين الفرعي إلى رمز المتصل.

يمين

لا يزال كود تشغيل RET في ARM 64 يتعامل مع الروتين الفرعي، ولكنه يعمل بشكل مختلف عن RTS في 6502 أو RET على x64، أو مجموعة 'BX LR' في ARM 64. في ARM 64، بناء جملة RET هو:

مستقيم {Xn}

تتيح هذه التعليمات الفرصة للبرنامج للاستمرار في روتين فرعي ليس هو الروتين الفرعي للمتصل، أو مجرد الاستمرار في بعض التعليمات الأخرى ومقطع التعليمات البرمجية التالي الخاص بها. Xn هو سجل للأغراض العامة يحمل العنوان الذي يجب أن يستمر البرنامج إليه. هذه التعليمات فروع دون قيد أو شرط. يتم تعيينه افتراضيًا على محتوى X30 إذا لم يتم إعطاء Xn.

معيار استدعاء الإجراء

إذا أراد المبرمج أن يتفاعل الكود الخاص به مع الكود الذي كتبه شخص آخر أو مع الكود الذي تم إنتاجه بواسطة مترجم، فيجب على المبرمج الاتفاق مع الشخص أو كاتب المترجم على قواعد استخدام السجل. بالنسبة لبنية ARM، تسمى هذه القواعد معيار استدعاء الإجراء أو PCS. هذه اتفاقيات بين طرفين أو ثلاثة أطراف. تحدد PCS ما يلي:

- ما هي سجلات μP المستخدمة لتمرير الوسائط إلى الوظيفة (الروتين الفرعي)

- ما هي سجلات μP المستخدمة لإرجاع النتيجة إلى الوظيفة التي تقوم بالاتصال والتي تعرف باسم المتصل

- أي μP يسجل الوظيفة التي يتم استدعاؤها، والتي تعرف باسم المستدعي، يمكن أن تفسد

- الذي يسجله μP لا يمكن أن يفسده المستدعى

6.49 المقاطعات

هناك نوعان من دوائر التحكم في المقاطعة المتوفرة لمعالج ARM:

- وحدة تحكم المقاطعة القياسية: يحدد معالج المقاطعة الجهاز الذي يتطلب الخدمة عن طريق قراءة سجل الصورة النقطية للجهاز في وحدة تحكم المقاطعة.

- وحدة تحكم المقاطعة المتجهية (VIC): تعطي الأولوية للمقاطعات وتبسط عملية تحديد الجهاز الذي تسبب في المقاطعة. بعد ربط الأولوية وعنوان المعالج بكل مقاطعة، يؤكد مركز VIC فقط إشارة المقاطعة للمعالج إذا كانت أولوية المقاطعة الجديدة أعلى من معالج المقاطعة الذي يتم تنفيذه حاليًا.

ملحوظة : الاستثناء يشير إلى الخطأ. التفاصيل الخاصة بوحدة تحكم المقاطعة المتجهة لجهاز كمبيوتر ARM 32 بت هي كما يلي (64 بت مشابه):

| الجدول 6.49.1 استثناء/مقاطعة متجه ARM للكمبيوتر 32 بت |

|||

|---|---|---|---|

| استثناء/مقاطعة | يد قصيرة | عنوان | العنوان العالي |

| إعادة ضبط | إعادة ضبط | 0x00000000 | 0xffff0000 |

| تعليمات غير محددة | صندوق الأمم المتحدة للديمقراطية | 0x00000004 | 0xffff0004 |

| مقاطعة البرامج | سوي | 0x00000008 | 0xffff0008 |

| إحباط الجلب المسبق | papt | 0x0000000ج | 0xffff000C |

| تاريخ الإجهاض | دابت | 0x00000010 | 0xffff0010 |

| محجوز | - | 0x00000014 | 0xffff0014 |

| طلب المقاطعة | IRQ | 0x00000018 | 0xffff0018 |

| طلب المقاطعة السريعة | فيق | 0x0000001C | 0xffff001C |

يبدو هذا مثل الترتيب للهندسة المعمارية 6502 حيث نمي , ر ، و IRQ يمكن أن تحتوي على مؤشرات في الصفحة صفر، وتكون الإجراءات المقابلة عالية في الذاكرة (ROM OS). وفيما يلي وصف موجز لصفوف الجدول السابق:

إعادة ضبط

يحدث هذا عندما يتم تشغيل المعالج. يقوم بتهيئة النظام وإعداد الأكوام لأوضاع المعالج المختلفة. إنه الاستثناء ذو الأولوية القصوى. عند الدخول إلى معالج إعادة التعيين، يكون CPSR في وضع SVC ويتم تعيين كل من بتات IRQ وFIQ على 1، مما يؤدي إلى إخفاء أي مقاطعات.

تاريخ الإجهاض

الأولوية الثانية. يحدث هذا عندما نحاول القراءة/الكتابة في عنوان غير صالح أو الوصول إلى إذن وصول خاطئ. عند الدخول إلى Data Abort Handler، سيتم تعطيل طلبات IRQ (مجموعة I-bit 1) وسيتم تمكين FIQ. يتم إخفاء أسئلة IRQs، ولكن يتم الاحتفاظ بأسئلة FIQ غير مقنعة.

فيق

يتم تعطيل المقاطعة ذات الأولوية العليا، IRQ & FIQs، حتى تتم معالجة FIQ.

IRQ

يتم إدخال المقاطعة ذات الأولوية العالية، معالج IRQ، فقط في حالة عدم وجود FIQ مستمر وإحباط البيانات.

إحباط الجلب المسبق

يشبه هذا عملية إجهاض البيانات ولكنه يحدث عند فشل جلب العنوان. عند الدخول إلى المعالج، يتم تعطيل طلبات المقاطعة (IRQs) ولكن تظل أسئلة الأسئلة المتكررة (FIQs) ممكنة ويمكن أن تحدث أثناء إحباط الجلب المسبق.

سوي

يحدث استثناء مقاطعة البرامج (SWI) عند تنفيذ تعليمات SWI وعدم وضع علامة على أي من الاستثناءات الأخرى ذات الأولوية الأعلى.

تعليمات غير محددة

يحدث استثناء التعليمات غير المحددة عندما تصل تعليمات غير موجودة في مجموعة تعليمات ARM أو Thumb إلى مرحلة التنفيذ لخط الأنابيب ولم يتم وضع علامة على أي من الاستثناءات الأخرى. هذه هي نفس أولوية SWI التي يمكن أن تحدث في وقت واحد. وهذا يعني أن التعليمات التي يتم تنفيذها لا يمكن أن تكون تعليمات SWI وتعليمات غير محددة في نفس الوقت.

معالجة استثناءات ARM

تحدث الأحداث التالية عند حدوث استثناء:

- قم بتخزين CPSR في SPSR الخاص بوضع الاستثناء.

- يتم تخزين جهاز الكمبيوتر في LR لوضع الاستثناء.

- يتم تعيين سجل الارتباط على عنوان محدد بناءً على التعليمات الحالية. على سبيل المثال: بالنسبة إلى ISR، LR = آخر تعليمات تم تنفيذها + 8.

- قم بتحديث CPSR حول الاستثناء.

- اضبط جهاز الكمبيوتر على عنوان معالج الاستثناء.

6.5 التعليمات والبيانات

تشير البيانات إلى المتغيرات (التسميات بقيمها) والمصفوفات والهياكل الأخرى المشابهة للمصفوفة. السلسلة تشبه مجموعة من الأحرف. تم رؤية مجموعة من الأعداد الصحيحة في أحد الفصول السابقة. تشير التعليمات إلى أكواد التشغيل ومعاملاتها. يمكن كتابة برنامج باستخدام أكواد التشغيل والبيانات الممزوجة في قسم واحد مستمر من الذاكرة. هذا النهج له عيوب ولكن لا ينصح به.

يجب كتابة البرنامج مع التعليمات أولا، تليها البيانات (جمع المسند هو البيانات). يمكن أن يكون الفصل بين التعليمات والبيانات بضع بايت فقط. بالنسبة للبرنامج، يمكن أن تكون كل من التعليمات والبيانات في قسم أو قسمين منفصلين في الذاكرة.

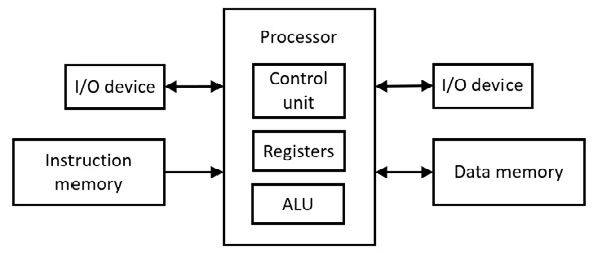

6.6 عمارة هارفارد

يُطلق على أحد أجهزة الكمبيوتر المبكرة اسم Harvard Mark I (1944). تستخدم بنية جامعة هارفارد الصارمة مساحة عنوان واحدة لتعليمات البرنامج ومساحة عنوان منفصلة مختلفة للبيانات. هذا يعني أن هناك ذاكرتين منفصلتين. ويبين ما يلي الهندسة المعمارية:

الشكل 6.71 هندسة هارفارد

تقوم وحدة التحكم بفك تشفير التعليمات. تقوم وحدة المنطق الحسابي (ALU) بإجراء العمليات الحسابية باستخدام المنطق التوافقي (البوابات). تقوم ALU أيضًا بالعمليات المنطقية (مثل التحويل).

مع المعالج الدقيق 6502، تنتقل التعليمات إلى المعالج الدقيق أولاً (وحدة التحكم) قبل أن ينتقل المرجع (المفرد للبيانات) إلى سجل μP قبل أن يتفاعلوا. ويحتاج هذا إلى نبضتين على مدار الساعة على الأقل ولا يمثل وصولاً متزامنًا إلى التعليمات ومسند البيانات. من ناحية أخرى، توفر بنية هارفارد الوصول المتزامن إلى التعليمات والبيانات، مع إدخال كل من التعليمات ومسند الإسناد إلى μP في نفس الوقت (رمز التشغيل إلى وحدة التحكم ومرجع الإسناد إلى تسجيل μP)، مما يوفر نبضة ساعة واحدة على الأقل. هذا هو شكل من أشكال التوازي. يتم استخدام هذا النوع من التوازي في ذاكرة التخزين المؤقت للأجهزة في اللوحات الأم الحديثة (راجع المناقشة التالية).

6.7 الذاكرة المؤقتة

ذاكرة التخزين المؤقت (RAM) هي منطقة ذاكرة عالية السرعة (مقارنة بسرعة الذاكرة الرئيسية) تقوم بتخزين تعليمات البرنامج أو البيانات مؤقتًا لاستخدامها في المستقبل. تعمل ذاكرة التخزين المؤقت بشكل أسرع من الذاكرة الرئيسية. عادة، يتم استرداد هذه التعليمات أو عناصر البيانات من الذاكرة الرئيسية الحديثة ومن المحتمل أن تكون هناك حاجة إليها مرة أخرى قريبًا. الغرض الأساسي من ذاكرة التخزين المؤقت هو زيادة سرعة الوصول المتكرر إلى نفس مواقع الذاكرة الرئيسية. لكي يكون فعالاً، يجب أن يكون الوصول إلى العناصر المخزنة مؤقتًا أسرع بكثير من الوصول إلى المصدر الأصلي للتعليمات أو البيانات والذي يشار إليه باسم مخزن النسخ الاحتياطية.

عندما يكون التخزين المؤقت قيد الاستخدام، تبدأ كل محاولة للوصول إلى موقع الذاكرة الرئيسي بالبحث في ذاكرة التخزين المؤقت. في حالة وجود العنصر المطلوب، يقوم المعالج باستعادته واستخدامه على الفور. وهذا ما يسمى ضربة ذاكرة التخزين المؤقت. إذا لم ينجح البحث في ذاكرة التخزين المؤقت (فقد ذاكرة التخزين المؤقت)، فيجب استرداد التعليمات أو عنصر البيانات من مخزن النسخ الاحتياطي (الذاكرة الرئيسية). أثناء عملية استرداد العنصر المطلوب، تتم إضافة نسخة إلى ذاكرة التخزين المؤقت للاستخدام المتوقع في المستقبل القريب.

وحدة إدارة الذاكرة

وحدة إدارة الذاكرة (MMU) هي دائرة تدير الذاكرة الرئيسية وسجلات الذاكرة ذات الصلة على اللوحة الأم. في الماضي، كانت عبارة عن دائرة متكاملة منفصلة على اللوحة الأم؛ ولكن اليوم، فهو عادةً جزء من المعالج الدقيق. يجب على MMU أيضًا إدارة ذاكرة التخزين المؤقت (الدائرة) والتي تعد أيضًا جزءًا من المعالج الدقيق اليوم. دائرة ذاكرة التخزين المؤقت هي دائرة متكاملة منفصلة في الماضي.

ذاكرة الوصول العشوائي الثابتة

تتمتع ذاكرة الوصول العشوائي الثابتة (SRAM) بوقت وصول أسرع بكثير من ذاكرة الوصول العشوائي الديناميكية، وإن كان ذلك على حساب دوائر أكثر تعقيدًا بشكل ملحوظ. تشغل خلايا البت SRAM مساحة أكبر بكثير على قالب الدائرة المتكاملة مقارنة بخلايا جهاز DRAM القادر على تخزين كمية مكافئة من البيانات. تتكون الذاكرة الرئيسية (RAM) عادةً من DRAM (ذاكرة الوصول العشوائي الديناميكية).

تعمل ذاكرة التخزين المؤقت على تحسين أداء الكمبيوتر لأن العديد من الخوارزميات التي يتم تنفيذها بواسطة أنظمة التشغيل والتطبيقات تظهر المنطقة المرجعية. تشير المنطقة المرجعية إلى إعادة استخدام البيانات التي تم الوصول إليها مؤخرًا. ويشار إلى هذا باسم المنطقة الزمنية. على اللوحة الأم الحديثة، توجد ذاكرة التخزين المؤقت في نفس الدائرة المتكاملة مثل المعالج الدقيق. الذاكرة الرئيسية (DRAM) بعيدة ويمكن الوصول إليها من خلال الحافلات. تشير المنطقة المرجعية أيضًا إلى المنطقة المكانية. تتعلق المنطقة المكانية بالسرعة العالية للوصول إلى البيانات بسبب القرب المادي.

كقاعدة عامة، تكون مناطق ذاكرة التخزين المؤقت صغيرة (من حيث عدد مواقع البايت) مقارنة بمخزن الدعم (الذاكرة الرئيسية). تم تصميم أجهزة ذاكرة التخزين المؤقت لتحقيق أقصى سرعة مما يعني عمومًا أنها أكثر تعقيدًا وتكلفة لكل بت من تقنية تخزين البيانات المستخدمة في مخزن النسخ الاحتياطي. نظرًا لحجمها المحدود، تميل أجهزة ذاكرة التخزين المؤقت إلى الامتلاء بسرعة. عندما لا تحتوي ذاكرة التخزين المؤقت على موقع متاح لتخزين إدخال جديد، يجب تجاهل الإدخال الأقدم. تستخدم وحدة التحكم في ذاكرة التخزين المؤقت سياسة استبدال ذاكرة التخزين المؤقت لتحديد إدخال ذاكرة التخزين المؤقت الذي سيتم الكتابة فوقه بواسطة الإدخال الجديد.

الهدف من ذاكرة التخزين المؤقت للمعالج الدقيق هو زيادة النسبة المئوية لذاكرة التخزين المؤقت بمرور الوقت، وبالتالي توفير أعلى معدل مستدام لتنفيذ التعليمات. ولتحقيق هذا الهدف، يجب أن يحدد منطق التخزين المؤقت التعليمات والبيانات التي سيتم وضعها في ذاكرة التخزين المؤقت والاحتفاظ بها للاستخدام في المستقبل القريب.

لا يضمن منطق التخزين المؤقت للمعالج أن عنصر البيانات المخزنة مؤقتًا سيتم استخدامه مرة أخرى بمجرد إدراجه في ذاكرة التخزين المؤقت.

يعتمد منطق التخزين المؤقت على احتمالية أنه نظرًا للمكان الزمني (التكرار مع مرور الوقت) والمكاني (المكاني)، هناك فرصة جيدة جدًا للوصول إلى البيانات المخزنة مؤقتًا في المستقبل القريب. في التطبيقات العملية على المعالجات الحديثة، تحدث عادةً عمليات الوصول إلى ذاكرة التخزين المؤقت بنسبة 95 إلى 97 بالمائة من عمليات الوصول إلى الذاكرة. نظرًا لأن زمن وصول ذاكرة التخزين المؤقت يمثل جزءًا صغيرًا من زمن وصول ذاكرة الوصول العشوائي الديناميكية (DRAM)، فإن معدل ضربات ذاكرة التخزين المؤقت المرتفع يؤدي إلى تحسين كبير في الأداء مقارنةً بالتصميم الخالي من ذاكرة التخزين المؤقت.

بعض التوازي مع ذاكرة التخزين المؤقت

كما ذكرنا سابقًا، فإن البرنامج الجيد الموجود في الذاكرة يحتوي على تعليمات منفصلة عن البيانات. في بعض أنظمة ذاكرة التخزين المؤقت، توجد دائرة ذاكرة تخزين مؤقت على 'يسار' المعالج، كما توجد دائرة ذاكرة تخزين مؤقت أخرى على 'يمين' المعالج. تعالج ذاكرة التخزين المؤقت اليسرى تعليمات البرنامج (أو التطبيق) وتتعامل ذاكرة التخزين المؤقت اليمنى مع بيانات نفس البرنامج (أو نفس التطبيق). وهذا يؤدي إلى زيادة السرعة بشكل أفضل.

6.8 العمليات والخيوط

تحتوي كل من أجهزة الكمبيوتر CISC وRISC على عمليات. هناك عملية على البرنامج. البرنامج الذي يتم تشغيله (التنفيذ) هو عملية. نظام التشغيل يأتي مع برامجه الخاصة. أثناء تشغيل الكمبيوتر، يتم أيضًا تشغيل برامج نظام التشغيل التي تمكن الكمبيوتر من العمل. هذه هي عمليات نظام التشغيل. يمكن للمستخدم أو المبرمج كتابة برامجه الخاصة. عندما يكون برنامج المستخدم قيد التشغيل، فهو عبارة عن عملية. لا يهم ما إذا كان البرنامج مكتوبًا بلغة التجميع أو بلغة عالية المستوى مثل C أو C++. تتم إدارة جميع العمليات (المستخدم أو نظام التشغيل) من خلال عملية أخرى تسمى 'المجدول'.

يشبه الخيط عملية فرعية تنتمي إلى العملية. يمكن أن تبدأ العملية وتنقسم إلى سلاسل ثم تستمر كعملية واحدة. يمكن اعتبار العملية التي لا تحتوي على خيوط بمثابة الخيط الرئيسي. تتم إدارة العمليات وخيوطها بواسطة نفس المجدول. المجدول نفسه هو برنامج عندما يكون مقيمًا في قرص نظام التشغيل. عند التشغيل في الذاكرة، يكون المجدول عبارة عن عملية.

6.9 المعالجة المتعددة

تتم إدارة المواضيع تقريبًا مثل العمليات. المعالجة المتعددة تعني تشغيل أكثر من عملية في نفس الوقت. هناك أجهزة كمبيوتر تحتوي على معالج دقيق واحد فقط. هناك أجهزة كمبيوتر تحتوي على أكثر من معالج دقيق. باستخدام معالج دقيق واحد، تستخدم العمليات و/أو الخيوط نفس المعالج الدقيق بطريقة التشذير (أو التقطيع الزمني). وهذا يعني أن العملية تستخدم المعالج وتتوقف دون الانتهاء. عملية أو خيط آخر يستخدم المعالج ويتوقف دون الانتهاء. ثم، تستخدم عملية أو خيط آخر المعالج الدقيق وتتوقف دون الانتهاء. ويستمر هذا حتى تحصل كافة العمليات والخيوط التي تم وضعها في قائمة الانتظار بواسطة المجدول على حصة من المعالج. ويشار إلى هذا باسم المعالجة المتعددة المتزامنة.

عندما يكون هناك أكثر من معالج دقيق واحد، تكون هناك معالجة متعددة متوازية، بدلاً من التزامن. في هذه الحالة، يقوم كل معالج بتشغيل عملية أو خيط معين، يختلف عما يقوم بتشغيله المعالج الآخر. تقوم جميع المعالجات الموجودة على نفس اللوحة الأم بتشغيل عملياتها المختلفة و/أو خيوطها المختلفة في نفس الوقت في معالجة متعددة متوازية. لا تزال العمليات والخيوط في المعالجة المتعددة المتوازية تتم إدارتها بواسطة المجدول. المعالجة المتعددة المتوازية أسرع من المعالجة المتعددة المتزامنة.

في هذه المرحلة، قد يتساءل القارئ كيف تكون المعالجة المتوازية أسرع من المعالجة المتزامنة. وذلك لأن المعالجات تشترك (يجب أن تستخدم في أوقات مختلفة) نفس الذاكرة ومنافذ الإدخال/الإخراج. حسنًا، مع استخدام ذاكرة التخزين المؤقت، يكون التشغيل العام للوحة الأم أسرع.

6.10 الترحيل

وحدة إدارة الذاكرة (MMU) هي دائرة قريبة من المعالج الدقيق أو في شريحة المعالج الدقيق. يتعامل مع خريطة الذاكرة أو الترحيل ومشكلات الذاكرة الأخرى. لا يحتوي جهاز 6502 μP ولا كمبيوتر Commodore-64 على وحدة MMU في حد ذاتها (على الرغم من أنه لا يزال هناك بعض إدارة الذاكرة في جهاز Commodore-64). يتعامل Commodore-64 مع الذاكرة عن طريق الترحيل حيث تكون كل صفحة 256 10 بايت طويلة (100 16 بايت طويلة). ولم يكن من الضروري التعامل مع الذاكرة عن طريق الترحيل. لا يزال من الممكن أن يحتوي فقط على خريطة ذاكرة ومن ثم البرامج التي تتلاءم مع مناطقها المحددة المختلفة. حسنًا، يعد الترحيل إحدى الطرق لتوفير الاستخدام الفعال للذاكرة دون وجود العديد من أقسام الذاكرة التي لا يمكن أن تحتوي على بيانات أو برنامج.

تم إصدار بنية الكمبيوتر x86 386 في عام 1985. ويبلغ عرض ناقل العناوين 32 بت. لذلك، ما مجموعه 2 32 = 4,294,967,296 مساحة عنوان ممكنة. مساحة العنوان هذه مقسمة إلى 1,048,576 صفحة = 1,024 كيلوبايت صفحة. وبهذا العدد من الصفحات، تتكون الصفحة الواحدة من 4096 بايت = 4 كيلوبايت. يعرض الجدول التالي صفحات العناوين الفعلية لبنية x86 32 بت:

| الجدول 6.10.1 الصفحات المادية القابلة للعنونة لبنية x86 |

||

|---|---|---|

| العناوين الأساسية 16 | الصفحات | العناوين الأساسية 10 |

| FFFFFF000 - FFFFFFFF | الصفحة 1,048,575 | 4,294,963,200 – 4,294,967,295 |

| FFFE000 – FFFFEFFF | الصفحة 1,044,479 | 4,294,959,104 – 4,294,963,199 |

| FFFD000 – FFFFDFFF | الصفحة 1,040,383 | 4,294,955,008 – 4,294,959,103 |

| | | | |

| | | |

| | | |

| 00002000 – 00002FFF | الصفحة 2 | 8,192 – 12,288 |

| 00001000 – 00001FFF | صفحة 1 | 4,096 – 8,191 |

| 00000000 – 00000FFF | الصفحة 0 | 0 – 4,095 |

التطبيق اليوم يتكون من أكثر من برنامج . يمكن أن يستغرق البرنامج الواحد أقل من صفحة (أقل من 4096) أو يمكن أن يستغرق صفحتين أو أكثر. لذلك، يمكن أن يأخذ التطبيق صفحة واحدة أو أكثر حيث يبلغ طول كل صفحة 4096 بايت. يمكن لأشخاص مختلفين كتابة طلب، مع تخصيص صفحة واحدة أو أكثر لكل شخص.

لاحظ أن الصفحة 0 تتراوح من 00000000H إلى 00000FFF

الصفحة 1 من 00001000H إلى 00001FFFH، الصفحة 2 من 00002000 ح – 00002ففف ح ، وما إلى ذلك وهلم جرا. بالنسبة لجهاز كمبيوتر 32 بت، يوجد سجلان 32 بت في المعالج لعنونة الصفحة الفعلية: أحدهما للعنوان الأساسي والآخر لعنوان الفهرس. للوصول إلى مواقع البايت في الصفحة 2، على سبيل المثال، يجب أن يكون السجل الخاص بالعنوان الأساسي هو 00002 ح وهي أول 20 بت (من اليسار) لعناوين البداية للصفحة 2. وباقي البتات في حدود 000 ح إلى FFF ح موجودة في السجل المسمى 'سجل الفهرس'. لذلك، يمكن الوصول إلى كافة وحدات البايت الموجودة في الصفحة بمجرد زيادة المحتوى في سجل الفهرس من 000 ح إلى FFF ح . تتم إضافة المحتوى الموجود في سجل الفهرس إلى المحتوى الذي لا يتغير في السجل الأساسي للحصول على العنوان الفعال. نظام عنونة الفهرس هذا ينطبق على الصفحات الأخرى.

ومع ذلك، ليست هذه هي الطريقة التي تتم بها كتابة برنامج لغة التجميع لكل صفحة. لكل صفحة، يكتب المبرمج الكود بدءًا من الصفحة 000 ح إلى صفحة FFF ح . نظرًا لأن التعليمات البرمجية في الصفحات المختلفة متصلة، يستخدم المترجم عنوان الفهرس لربط جميع العناوين ذات الصلة في الصفحات المختلفة. على سبيل المثال، بافتراض أن الصفحة 0 والصفحة 1 والصفحة 2 مخصصة لتطبيق واحد ولكل منها الرقم 555 ح العنوان المتصل ببعضه البعض، يقوم المترجم بتجميعه بطريقة أنه عندما يكون 555 ح من الصفحة 0 يجب الوصول إليها، 00000 ح سيكون في السجل الأساسي و 555 ح سيكون في سجل الفهرس. متى 555 ح من الصفحة 1 يجب الوصول إليها، 00001 ح سيكون في السجل الأساسي و 555 ح سيكون في سجل الفهرس. متى 555 ح من الصفحة 2 يجب الوصول إليها، 00002 ح سيكون في السجل الأساسي وسيكون 555H في سجل الفهرس. وهذا ممكن لأنه يمكن تحديد العناوين باستخدام التسميات (المتغيرات). يجب أن يتفق المبرمجون المختلفون على اسم التسميات التي سيتم استخدامها لعناوين الاتصال المختلفة.

صفحة الذاكرة الافتراضية

يمكن تعديل الترحيل، كما هو موضح سابقًا، لزيادة حجم الذاكرة بتقنية يشار إليها باسم 'الذاكرة الافتراضية للصفحة'. على افتراض أن جميع صفحات الذاكرة الفعلية، كما هو موضح سابقًا، بها شيء ما (تعليمات وبيانات)، فليست كل الصفحات نشطة حاليًا. يتم إرسال الصفحات غير النشطة حاليًا إلى القرص الثابت ويتم استبدالها بالصفحات الموجودة على القرص الثابت التي تحتاج إلى التشغيل. وبهذه الطريقة يزداد حجم الذاكرة. مع استمرار تشغيل الكمبيوتر، يتم تبديل الصفحات التي تصبح غير نشطة مع الصفحات الموجودة على القرص الثابت والتي قد تظل هي الصفحات التي تم إرسالها من الذاكرة إلى القرص. كل هذا يتم بواسطة وحدة إدارة الذاكرة (MMU).

6.11 المشاكل

يُنصح القارئ بحل جميع المشكلات الموجودة في الفصل قبل الانتقال إلى الفصل التالي.

1) اذكر أوجه التشابه والاختلاف بين بنيات الكمبيوتر CISC وRISC. قم بتسمية مثال واحد لكل من كمبيوتر SISC وRISC.

2) أ) ما هي الأسماء التالية لجهاز الكمبيوتر CISC من حيث البتات: بايت، كلمة، كلمة مزدوجة، كلمة رباعية، وكلمة رباعية مزدوجة.

ب) ما هي الأسماء التالية لجهاز الكمبيوتر RISC من حيث البتات: بايت، نصف كلمة، كلمة، وكلمة مزدوجة.

ج) نعم أم لا. هل تعني الكلمات المزدوجة والكلمات الرباعية نفس الأشياء في معماريتي CISC وRISC؟

3 أ) بالنسبة لـ x64، يتراوح عدد البايتات لتعليمات لغة التجميع من ماذا إلى ماذا؟

ب) هل عدد البايتات لجميع تعليمات لغة التجميع الخاصة بـ ARM 64 ثابت؟ إذا كانت الإجابة بنعم، ما هو عدد البايتات لجميع التعليمات؟

4) قم بإدراج تعليمات لغة التجميع الأكثر استخدامًا لـ x64 ومعانيها.

5) قم بإدراج تعليمات لغة التجميع الأكثر استخدامًا لـ ARM 64 ومعانيها.

6) ارسم مخططًا تخطيطيًا مسمىًا لجهاز الكمبيوتر القديم Harvard Architecture. اشرح كيفية استخدام تعليماته وميزات البيانات في ذاكرة التخزين المؤقت لأجهزة الكمبيوتر الحديثة.

7) التمييز بين العملية والخيط وإعطاء اسم العملية التي تتعامل مع العمليات والخيوط في معظم أنظمة الكمبيوتر.

8) اشرح بإيجاز ما هي المعالجة المتعددة.

9) أ) شرح الترحيل كما هو مطبق على بنية الكمبيوتر x86 386 μP.

ب) كيف يمكن تعديل هذا الترحيل لزيادة حجم الذاكرة بأكملها؟